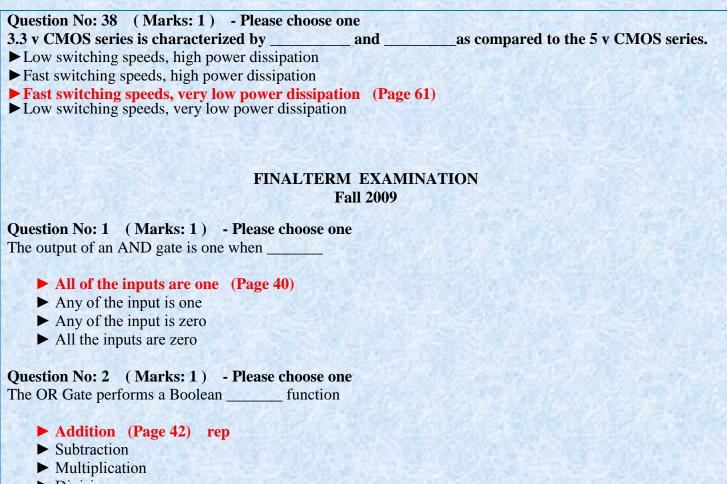

## Question No: 5 (Marks: 1) - Please choose one

The minimum time for which the input signal has to be maintained at the input of flip-flop is called \_\_\_\_\_\_ of the flip-flop.

- ► Set-up time

- ► Hold time (Page 242)

- Pulse Interval time

- Pulse Stability time (PST)

#### Question No: 6 (Marks: 1) - Please choose one

74HC163 has two enable input pins which are \_\_\_\_\_ and \_\_\_\_\_

- **ENP, ENT** (Page 285)

- ► ENI, ENC

- ► ENP, ENC

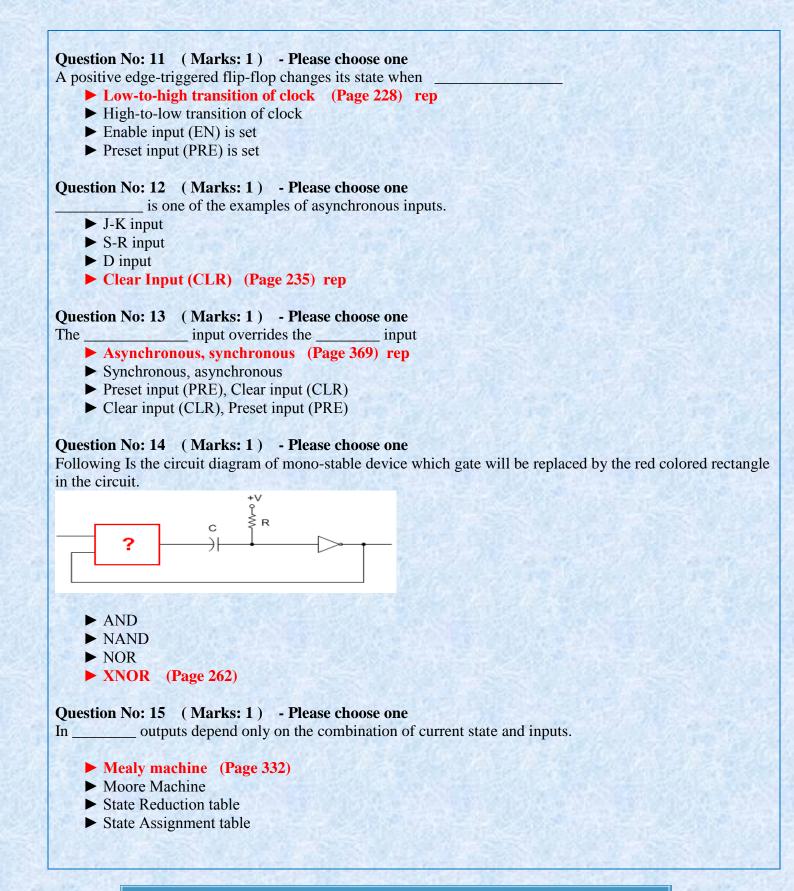

- ► ENT, ENI

#### Question No: 7 (Marks: 1) - Please choose one

\_\_\_\_\_ is said to occur when multiple internal variables change due to change in one input variable

- ► Clock Skew

- ► Race condition (Page 267)

- ► Hold delay

- ► Hold and Wait

# Question No: 8(Marks: 1)- Please choose oneTheinput overrides theinput

#### ► Asynchronous, synchronous (Page 369)

- Synchronous, asynchronous

- Preset input (PRE), Clear input (CLR)

- Clear input (CLR), Preset input (PRE)

#### Question No: 9 (Marks: 1) - Please choose one

- A decade counter is \_\_\_\_

- ► Mod-3 counter

- ► Mod-5 counter

- ► Mod-8 counter

- ► Mod-10 counter (Page 274)

**Question No: 10 (Marks: 1) - Please choose one** In asynchronous transmission when the transmission line is idle, \_\_\_\_\_

- ► It is set to logic low

- ► It is set to logic high (Page 356)

- Remains in previous state

- ► State of transmission line is not used to start transmission

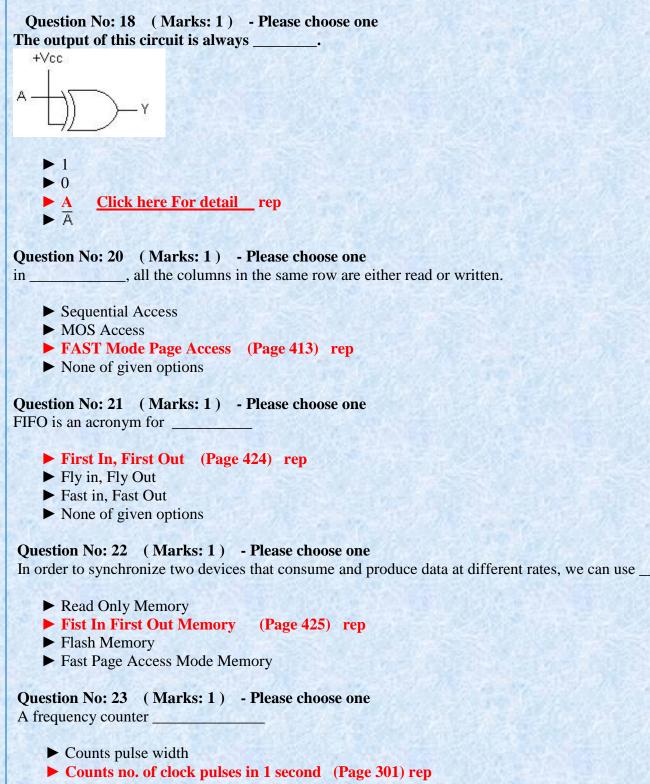

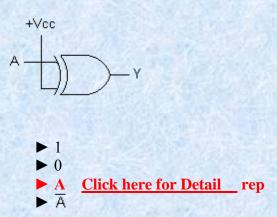

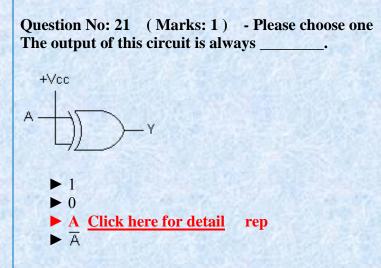

Question No: 11 (Marks: 1) - Please choose one A Nibble consists of \_\_\_\_\_ bits ▶ 2 ▶ 4 (Page 394) ▶ 8 ▶ 16 **Question No: 12** (Marks: 1) - Please choose one The output of this circuit is always \_\_\_\_\_. +Vcc ▶ 1 . 0 **Click here for detail** A ► Ā Question No: 13 (Marks: 1) - Please choose one Excess-8 code assigns to "-8" ▶ 1110 ▶ 1100

▶ 1000

▶ 0000 (Page 34)

**Question No: 14** (Marks: 1) - Please choose one The voltage gain of the Inverting Amplifier is given by the relation \_\_\_\_\_

Vout / Vin = - Rf / Ri (Page 446)

Vout / Rf = - Vin / Ri

Rf / Vin = - Ri / Vout

Rf / Vin = Ri / Vout

Question No: 15 (Marks: 1) - Please choose one LUT is acronym for \_\_\_\_\_

#### Look Up Table (Page 439)

- Local User Terminal

- ► Least Upper Time Period

- None of given options

Question No: 16 (Marks: 1) - Please choose one The three fundamental gates are \_\_\_\_\_

- ► AND, NAND, XOR

- ► OR, AND, NAND

- ► NOT, NOR, XOR

- ▶ NOT, OR, AND (Page 40)

## Question No: 17 (Marks: 1) - Please choose one

The total amount of memory that is supported by any digital system depends upon \_\_\_\_\_

- ► The organization of memory

- ► The structure of memory

- ► The size of decoding unit

- ► The size of the address bus of the microprocessor (Page 430)

## Question No: 18 (Marks: 1) - Please choose one

Stack is an acronym for \_\_\_\_\_

- ► FIFO memory

- LIFO memory (Page 429)

- ► Flash Memory

- Bust Flash Memory

# Question No: 19 (Marks: 1) - Please choose one

Addition of two octal numbers "36" and "71" results in \_\_\_\_\_

- ▶ 213

- ▶ 123

- ▶ 127

- ▶ 345

## Question No: 20 (Marks: 1) - Please choose one

\_\_\_\_\_ is one of the examples of synchronous inputs.

- ► J-K input (Page 235)

- ► EN input

- Preset input (PRE)

- ► Clear Input (CLR)

# Question No: 21 (Marks: 1) - Please choose one

\_\_\_\_\_occurs when the same clock signal arrives at different times at different clock inputs due to propagation delay.

- Race condition

- Clock Skew (Page 226)

- ► Ripple Effect

- ► None of given options

## Question No: 22 (Marks: 1) - Please choose one

Consider an up/down counter that counts between 0 and 15, if external input(X) is "0" the counter counts upward (0000 to 1111) and if external input (X) is "1" the counter counts downward (1111 to 0000), now suppose that the present state is "1100" and X=1, the next state of the counter will be

```

0000

1101 (not sure)

1011

1111

```

#### Question No: 23 (Marks: 1) - Please choose one

In a state diagram, the transition from a current state to the next state is determined by

- Current state and the inputs (Page 332)

- Current state and outputs

- Previous state and inputs

- ► Previous state and outputs

#### Question No: 24 (Marks: 1) - Please choose one

\_ is used to simplify the circuit that determines the next state.

- State diagram

- ► Next state table

- State reduction

- ► State assignment (Page 335)

#### Question No: 25 (Marks: 1) - Please choose one

A 8-bit serial in / parallel out shift register contains the value "8", \_\_\_\_\_ clock signal(s) will be required to shift the value completely out of the register.

1

2

4

8 (Page 356) rep

#### Question No: 26 (Marks: 1) - Please choose one

Assume that a 4-bit serial in/serial out shift register is initially clear. We wish to store the nibble 1100. What will be the 4-bit pattern after the second clock pulse? (Right-most bit first.)

**Question No: 27** (Marks: 1) - Please choose one LUT is acronym for \_\_\_\_\_

- ► Look Up Table (Page 439) rep

- Local User Terminal

- ► Least Upper Time Period

- ► None of given options

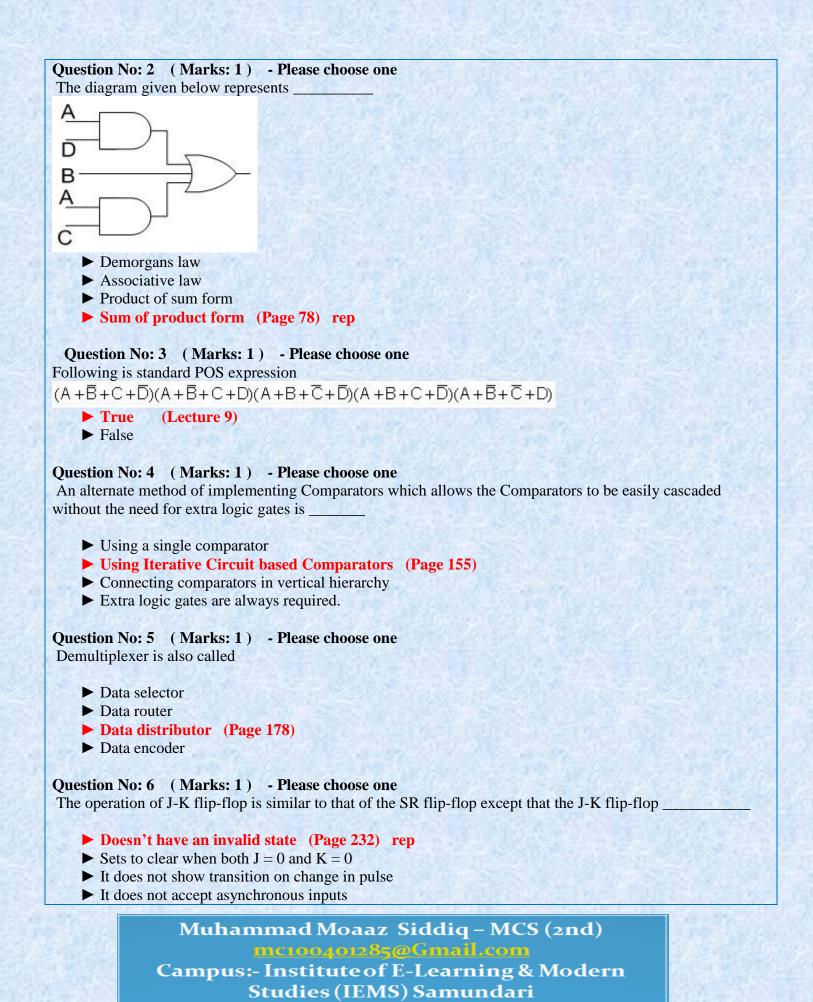

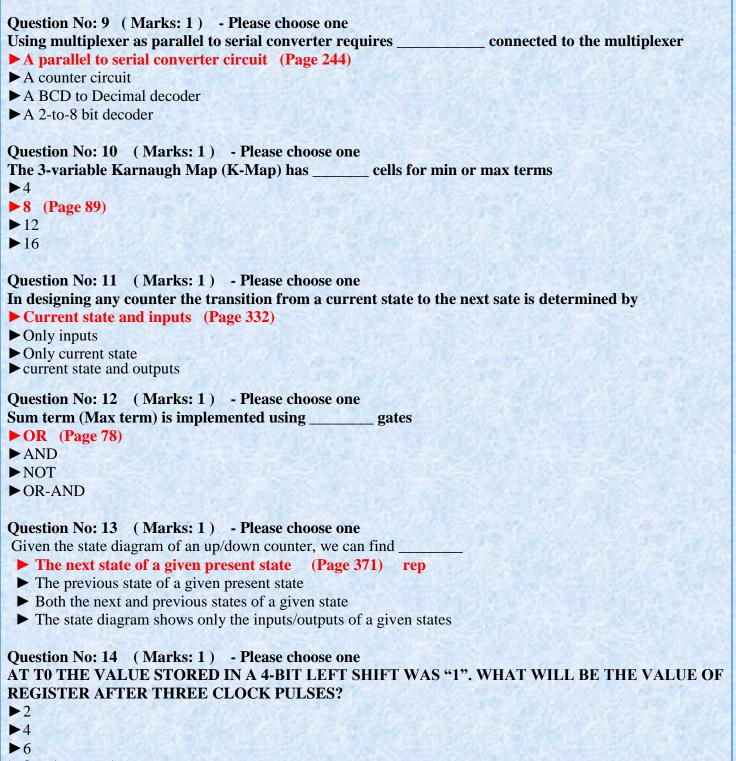

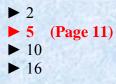

. Question No: 28 (Marks: 1) - Please choose one The diagram given below represents \_\_\_\_\_

- ► Associative law

- ▶ Product of sum form

- **Sum of product form** (Page 78)

## Question No: 29 (Marks: 1) - Please choose one

The operation of J-K flip-flop is similar to that of the SR flip-flop except that the J-K flip-flop

## ► Doesn't have an invalid state (Page 232)

- Sets to clear when both J = 0 and K = 0

- ► It does not show transition on change in pulse

- ► It does not accept asynchronous inputs

#### Question No: 30 (Marks: 1) - Please choose one

A multiplexer with a register circuit converts \_\_\_\_\_

- Serial data to parallel

- Parallel data to serial (Page 356) rep

- Serial data to serial

- ► Parallel data to parallel

**Question No: 31 (Marks: 1) - Please choose one** A GAL is essentially a \_\_\_\_\_.

- ► Non-reprogrammable PAL

- ▶ PAL that is programmed only by the manufacturer

- ► Very large PAL

- Reprogrammable PAL (Page 183)

Muhammad Moaaz Siddiq – MCS (2nd) mc100401285@Gmail.com Campus:- Institute of E-Learning & Modern

Studies (IEMS) Samundari

### Question No: 32 (Marks: 1) - Please choose one

in \_\_\_\_\_, all the columns in the same row are either read or written.

- Sequential Access

- ► MOS Access

- ► FAST Mode Page Access (Page 413)

- None of given options

### Question No: 33 (Marks: 1) - Please choose one

In order to synchronize two devices that consume and produce data at different rates, we can use \_\_\_\_

- ► Read Only Memory

- ► Fist In First Out Memory (Page 425)

- ► Flash Memory

- ► Fast Page Access Mode Memory

## Question No: 34 (Marks: 1) - Please choose one

A positive edge-triggered flip-flop changes its state when \_\_\_\_\_

- ► Low-to-high transition of clock (Page 228)

- ► High-to-low transition of clock

- ► Enable input (EN) is set

- ▶ Preset input (PRE) is set

## FINALTERM EXAMINATION Spring 2010

#### Question No: 1 (Marks: 1) - Please choose one

A 8-bit serial in / parallel out shift register contains the value "8", \_\_\_\_\_ clock signal(s) will be required to shift the value completely out of the register.

1

2

4

8 (Page 356) rep

Question No: 2 (Marks: 1) - Please choose one A frequency counter

- ► Counts pulse width

- ► Counts no. of clock pulses in 1 second (Page 301)

- Counts high and low range of given clock pulse

- None of given options

```

Question No: 3 (Marks: 1) - Please choose one

In a sequential circuit the next state is determined by ______ and _

► State variable, current state

Current state, flip-flop output

► Current state and external input

► Input and clock signal applied (Page 305)

Question No: 4 (Marks: 1) - Please choose one

The divide-by-60 counter in digital clock is implemented by using two cascading counters:

▶ Mod-6, Mod-10 (Page 229) rep

▶ Mod-50, Mod-10

▶ Mod-10, Mod-50

▶ Mod-50, Mod-6

Question No: 5 (Marks: 1) - Please choose one

In NOR gate based S-R latch if both S and R inputs are set to logic 0, the previous output state is maintained.

► True (Page 221) rep

► False

Question No: 6 (Marks: 1) - Please choose one

Flip flops are also called

► Bi-stable dualvibrators

► Bi-stable transformer

► Bi-stable multivibrators (Page 228)

Bi-stable singlevibrators

Question No: 7 (Marks: 1) - Please choose one

The minimum time for which the input signal has to be maintained at the input of flip-flop is called _____ of

the flip-flop.

► Set-up time

```

- ► Hold time (Page 242) rep

- Pulse Interval time

- ► Pulse Stability time (PST)

**Question No: 8** (Marks: 1) - Please choose one 74HC163 has two enable input pins which are \_\_\_\_\_ and \_\_\_\_\_

- **ENP, ENT** (Page 285)

- ► ENI, ENC

- ► ENP, ENC

- ► ENT, ENI

```

Question No: 14 (Marks: 1) - Please choose one

In asynchronous transmission when the transmission line is idle,

► It is set to logic low

▶ It is set to logic high (Page 356) rep

Remains in previous state

State of transmission line is not used to start transmission

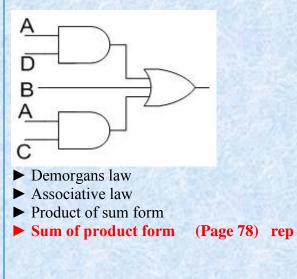

Ouestion No: 15 (Marks: 1) - Please choose one

A Nibble consists of _____ bits

▶ 2

▶ 4 (Page 394)

▶ 8

▶ 16

Question No: 16 (Marks: 1) - Please choose one

The output of this circuit is always

+Vcc

A

▶ 1

▶ 0

Click here for detail

rep

A

A

Question No: 17 (Marks: 1) - Please choose one

Excess-8 code assigns _____ to "-8"

▶ 1110

▶ 1100

▶ 1000

▶ 0000

(Page 34)

rep

Ouestion No: 18 (Marks: 1) - Please choose one

The voltage gain of the Inverting Amplifier is given by the relation _

```

V<sub>out</sub> / V<sub>in</sub> = - R<sub>f</sub> / R<sub>i</sub> (Page 446)

V<sub>out</sub> / R<sub>f</sub> = - V<sub>in</sub> / R<sub>i</sub>

R<sub>f</sub> / V<sub>in</sub> = - R<sub>i</sub> / V<sub>out</sub>

R<sub>f</sub> / V<sub>in</sub> = R<sub>i</sub> / V<sub>out</sub>

**Question No: 19** (Marks: 1) - Please choose one LUT is acronym for \_\_\_\_\_

- Look Up Table (Page 439) rep

- Local User Terminal

- ► Least Upper Time Period

- None of given options

Question No: 20 (Marks: 1) - Please choose one DRAM stands for \_\_\_\_\_

- ► Dynamic RAM (Page 407)

- ► Data RAM

- Demoduler RAM

- None of given options

**Question No: 21** (Marks: 1) - Please choose one The three fundamental gates are \_\_\_\_\_

- ► AND, NAND, XOR

- ► OR, AND, NAND

- ► NOT, NOR, XOR

- ► NOT, OR, AND (Page 40)

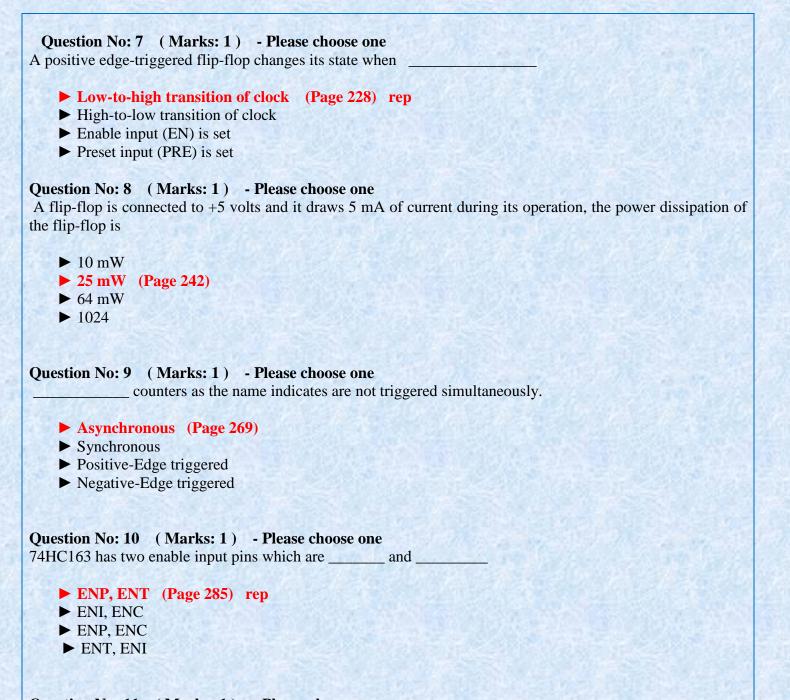

Question No: 22 (Marks: 1) - Please choose one

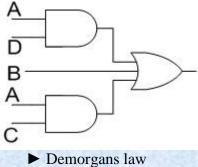

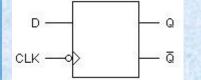

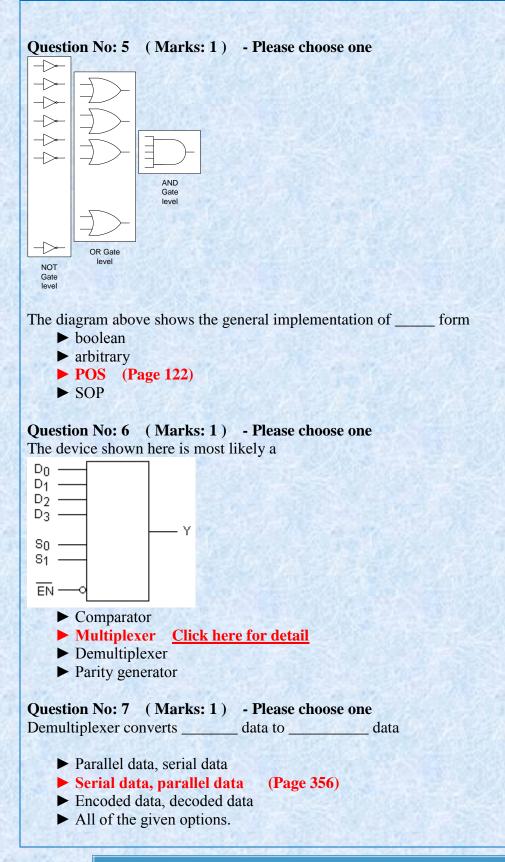

Which of the following statement is true regarding above block diagram?

- ► Triggering takes place on the negative-going edge of the CLK pulse

- ► Triggering takes place on the positive-going edge of the CLK pulse

- ▶ Triggering can take place anytime during the HIGH level of the CLK waveform

- ► Triggering can take place anytime during the LOW level of the CLK waveform

#### Question No: 23 (Marks: 1) - Please choose one

The total amount of memory that is supported by any digital system depends upon \_\_\_\_\_

- ► The organization of memory

- ► The structure of memory

- ► The size of decoding unit

- ► The size of the address bus of the microprocessor (Page 430) rep

Question No: 3 (Marks: 1) - Please choose one The basic building block for a logical circuit is

- ► A Flip-Flop

- ► A Logical Gate (Page 7)

- ► An Adder

None of given options

## Question No: 4 (Marks: 1) - Please choose one

The output of the expression F=A.B.C will be Logic \_\_\_\_\_ when A=1, B=0, C=1.

- ► Undefined

- ► One

▶ 2 ▶ 8

Zero (According to rule)

▶ No Output as input is invalid.

#### Question No: 5 (Marks: 1) - Please choose one

\_ is invalid number of cells in a single group formed by the adjacent cells in K-map

▶ 12 (According to rule "2^n") ▶ 16

## Question No: 6 (Marks: 1) - Please choose one

The PROM consists of a fixed non-programmable \_\_\_\_\_\_ Gate array configured as a decoder.

- ► AND (Page 182)

- ► OR

- ► NOT

- ► XOR

#### Question No: 7 (Marks: 1) - Please choose one

\_ is one of the examples of synchronous inputs.

► J-K input (Page 235) rep

- ► EN input

- ▶ Preset input (PRE)

- Clear Input (CLR)

Question No: 8 (Marks: 1) - Please choose one is one of the examples of asynchronous inputs.

- ► J-K input

- ► S-R input

- ► D input

- Clear Input (CLR) (Page 235)

▶ 1011▶ 11111

#### Question No: 12 (Marks: 1) - Please choose one

In a state diagram, the transition from a current state to the next state is determined by

#### Current state and the inputs (Page 232)

- Current state and outputs

- ▶ Previous state and inputs

- Previous state and outputs

#### Question No: 13 (Marks: 1) - Please choose one

\_ is used to minimize the possible no. of states of a circuit.

- ► State assignment (Page 341)

- ► State reduction

- Next state table

- State diagram

mc100401285@Gmail.com Campus:- Institute of E-Learning & Modern Studies (IEMS) Samundari

```

Question No: 19 (Marks: 1) - Please choose one

Assume that a 4-bit serial in/serial out shift register is initially clear. We wish to store the nibble 1100.

What will be the 4-bit pattern after the second clock pulse? (Right-most bit first.)

▶ 1100

▶ 0011

▶ 0000

Click here for detail rep

▶ 1111

Question No: 20 (Marks: 1) - Please choose one

The address from which the data is read, is provided by

Depends on circuitry

► None of given options

► RAM

► Microprocessor (Page 397)

Question No: 21 (Marks: 1) - Please choose one

FIFO is an acronym for _

▶ First In, First Out (Page 424)

► Fly in, Fly Out

► Fast in, Fast Out

► None of given options

Question No: 22 (Marks: 1) - Please choose one

LUT is acronym for ____

► Look Up Table (Page 439) rep

Local User Terminal

► Least Upper Time Period

None of given options

Question No: 23 (Marks: 1) - Please choose one

The voltage gain of the Inverting Amplifier is given by the relation _

\blacktriangleright V<sub>out</sub> / V<sub>in</sub> = - R<sub>f</sub> / R<sub>i</sub>

(Page 446)

\blacktriangleright V<sub>out</sub> / R<sub>f</sub> = - V<sub>in</sub> / R<sub>i</sub>

\blacktriangleright R<sub>f</sub> / V<sub>in</sub> = - R<sub>i</sub> / V<sub>out</sub>

\blacktriangleright R<sub>f</sub> / V<sub>in</sub> = R<sub>i</sub> / V<sub>out</sub>

```

#### Question No: 24 (Marks: 1) - Please choose one

\_\_\_\_\_ of a D/A converter is determined by comparing the actual output of a D/A converter with the expected output.

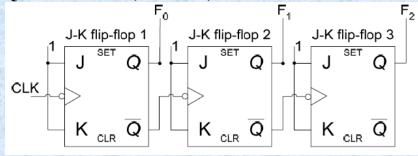

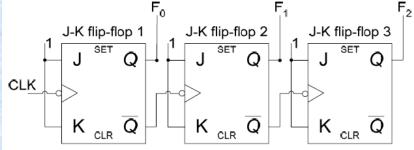

#### Question No: 25 (Marks: 1) - Please choose one

Above is the circuit diagram of \_

#### ► Asynchronous up-counter (Page 270)

- ► Asynchronous down-counter

- ► Synchronous up-counter

- Synchronous down-counter

#### Question No: 26 (Marks: 1) - Please choose one

The sequence of states that are implemented by a n-bit Johnson counter is

▶ n+2 (n plus 2)

## ▶ 2n (n multiplied by 2) (Page 354)

- $\blacktriangleright 2^n$  (2 raise to power n)

- $\blacktriangleright$  n<sup>2</sup> (n raise to power 2)

#### FINALTERM EXAMINATION Spring 2010

Question No: 1 (Marks: 1) - Please choose one "A + B = B + A" is \_\_\_\_\_

- ► Demorgan's Law

- Distributive Law

- ► Commutative Law (Page 72)

- Associative Law

Question No: 11 (Marks: 1) - Please choose one The divide-by-60 counter in digital clock is implemented by using two cascadi

The divide-by-60 counter in digital clock is implemented by using two cascading counters:

- Mod-6, Mod-10 (Page 299)

Mod-50, Mod-10

Mod-10, Mod-50

- ▶ Mod-50, Mod-6

```

Question No: 12 (Marks: 1) - Please choose one

```

In a state diagram, the transition from a current state to the next state is determined by

- Counts high and low range of given clock pulse

- None of given options

**Question No: 24** (Marks: 1) - Please choose one The sequence of states that are implemented by a n-bit Johnson counter is

n+2 (n plus 2)

2n (n multiplied by 2) (Page 354) rep

2<sup>n</sup> (2 raise to power n)

n<sup>2</sup> (n raise to power 2)

Question No: 25 (Marks: 1) - Please choose one Stack is an acronym for \_\_\_\_\_

- FIFO memory

LIFO memory (Page 429) rep

- ► Flash Memory

- Bust Flash Memory

**Question No: 26 (Marks: 1) - Please choose one** The 4-bit 2's complement representation of "+5" is \_\_\_\_\_

- ▶ 1010

- ▶ 1110

- ▶ 1011

- ▶ 0101 (Page 22)

## FINALTERM EXAMINATION Spring 2010

Question No: 1 (Marks: 1) - Please choose one The storage cell in SRAM is > a flip –flop > a capacitor (Page 407) > a fuse > a magnetic domain

Question No: 2 (Marks: 1) - Please choose one What is the difference between a D latch and a D flip-flop?

- ▶ The D latch has a clock input.

- ▶ The D flip-flop has an enable input.

- The D latch is used for faster operation.

► The D flip-flop has a clock input. <u>Click here for detail</u>

```

Ouestion No: 3 (Marks: 1) - Please choose one

For a positive edge-triggered J-K flip-flop with both J and K HIGH, the outputs will

if the clock

goes HIGH.

toggle

Click here for detail

▶ set

reset

▶ not change

Ouestion No: 4 (Marks: 1) - Please choose one

The OR gate performs Boolean

▶ multiplication

▶ subtraction

► division

▶ addition (Page 42)

Ouestion No: 5 (Marks: 1) - Please choose one

```

If an S-R latch has a 1 on the S input and a 0 on the R input and then the S input goes to 0, the latch will be

▶ set (Page 219)

► reset

▶ invalid

▶ clear

5. Determine the values of A, B, C, and D that make the sum term A(bar) + B+C(bar)+D equal to zero.

A = 1, B = 0, C = 0, D = 0

A = 1, B = 0, C = 1, D = 0 (Lecture 8)

A = 0, B = 1, C = 0, D = 0

A = 1, B = 0, C = 1, D = 1

Question No: 6 (Marks: 1) - Please choose one The power dissipation, *PD*, of a logic gate is the product of the ▶ dc supply voltage and the peak current <u>Click here for detail</u>

► dc supply voltage and the average supply current

► ac supply voltage and the peak current

► ac supply voltage and the average supply current

Question No: 7 (Marks: 1) - Please choose one A Karnaugh map is similar to a truth table because it presents all the possible values of input variables and the resulting output of each value.

True <u>Click here for detail</u>

False

Question No: 8 (Marks: 1) - Please choose one NOR Gate can be used to perform the operation of AND, OR and NOT Gate True (Page 50) False

▶8 (not sure)

Question No: 15 (Marks: 1) - Please choose one WHEN BOTH THE INPUTS OF EDGE-TRIGGERED J-K FLOP-FLOP ARE SET TO LOGIC ZERO ► THE FLOP-FLOP IS TRIGGERED ► O=0 AND O'=1 ► Q=1 AND Q'=0 (Page 233) ► THE OUTPUT OF FLIP-FLOP REMAINS UNCHANGED **Ouestion No: 16** (Marks: 1) - Please choose one If S=1 and R=0, then Q(t+1) = for positive edge triggered flip-flop ▶0 ▶1 (Page 230) ► Invalid ► Input is invalid If S=1 and R=1, then O(t+1) = for negative edge triggered flip-flop ▶ 0 ▶ 1 ► Invalid (Page 233) ▶ Input is invalid Question No: 17 (Marks: 1) - Please choose one The minimum time for which the input signal has to be maintained at the input of flip-flop is called of the flip-flop. ► Set-up time ► Hold time (Page 242) rep ► Pulse Interval time ► Pulse Stability time (PST) **Question No: 18** (Marks: 1) - Please choose one We have a digital circuit. Different parts of circuit operate at different clock frequencies (4MHZ, 2MHZ and 1MHZ), but we have a single clock source having a fix clock frequency (4MHZ), we can get help by ► Using S-R Flop-Flop ► D-flipflop ► J-K flip-flop (Page 252) ► T-Flip-Flop Question No: 19 (Marks: 1) - Please choose one A counter is implemented using three (3) flip-flops, possibly it will have maximum output status.

```

3

7

8 (Page 272)

15

```

Question No: 20 (Marks: 1) - Please choose one

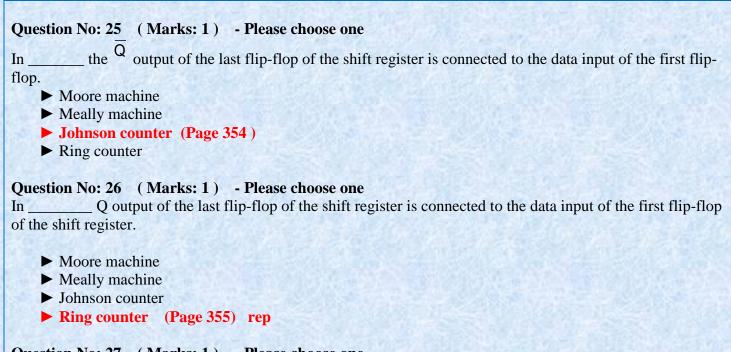

In \_\_\_\_\_\_ Q output of the last flip-flop of the shift register is connected to the data input of the first flip-flop of the shift register.

► Moore machine

► Meally machine

► Johnson counter

► Ring counter (Page 355)

Question No: 21 (Marks: 1) - Please choose one The \_\_\_\_\_\_ of a ROM is the time it takes for the data to appear at the Data Output of the ROM chip after an address is applied at the address input lines

► Write Time

► Recycle Time

► Refresh Time

► Access Time (Page 417)

Question No: 22 (Marks: 1) - Please choose one

Bi-stable devices remain in either of their \_\_\_\_\_\_ states unless the inputs force the device to switch its state

► Ten

► Eight

► Three

► Two (Page 262)

Question No: 23 (Marks: 1) - Please choose one

occurs when the same clock signal arrives at different times at different clock inputs due to propagation delay.

► Race condition

- Clock Skew (Page 226) rep

- ► Ripple Effect

► None of given options

Question No: 24 (Marks: 1) - Please choose one The alternate solution for a multiplexer and a register circuit is \_\_\_\_\_\_

# ► Parallel in / Serial out shift register (Page 356)

Serial in / Parallel out shift register

- ► Parallel in / Parallel out shift register

- ► Serial in / Serial Out shift register

## Question No: 25 (Marks: 1) - Please choose one

Stack is an acronym for \_\_\_\_\_

- ► FIFO memory

- LIFO memory (Page 429) rep

- ► Flash Memory

- Bust Flash Memory

Question No: 26 (Marks: 1) - Please choose one A full-adder has a Cin = 0. What are the sum (<PRIVATE ''TYPE=PICT;ALT=sigma''>) and the carry (Cout) when A = 1 and B = 1? >= 0, Cout = 0 >= 0, Cout = 1 (Page 135) >= 1, Cout = 0 >= 1, Cout = 1

Question No: 27 (Marks: 1) - Please choose one THE GLITCHES DUE TO RACE CONDITION CAN BE AVOIDED BY USING A \_\_\_\_ ▶ GATED FLIP-FLOPS ▶ PULSE TRIGGERED FLIP-FLOPS

▶ POSITIVE-EDGE TRIGGERED FLIP-FLOPS

► NEGATIVE-EDGE TRIGGERED FLIP-FLOPS (Page 267)

Question No: 28 (Marks: 1) - Please choose one The design and implementation of synchronous counters start from

- ► Truth table

- ► k-map

- ► state table

- ▶ state diagram (Page 319)

Question No: 29 (Marks: 1) - Please choose one THE HOURS COUNTER IS IMPLEMENTED USING \_\_\_\_ ▶ ONLY A SINGLE MOD-12 COUNTER IS REQUIRED ▶ MOD-10 AND MOD-6 COUNTERS

► MOD-10 AND MOD-2 COUNTERS

► A SINGLE DECADE COUNTER AND A FLIP-FLOP (Page 299)

Question No: 30 (Marks: 1) - Please choose one

Given the state diagram of an up/down counter, we can find \_

The next state of a given present state (Page 371) rep

- ► The previous state of a given present state

- ► Both the next and previous states of a given state

- ► The state diagram shows only the inputs/outputs of a given states

## Question No: 31 (Marks: 1) - Please choose one

LUT is acronym for \_\_\_\_

- ► Look Up Table (Page 439) rep

- Local User Terminal

- ► Least Upper Time Period

- None of given options

#### Question No: 32 (Marks: 1) - Please choose one

\_\_\_\_\_ of a D/A converter is determined by comparing the actual output of a D/A converter with the expected output.

► Resolution ► Accuracy (Page 460) rep ► Quantization ► Missing Code **Question No: 33** (Marks: 1) - Please choose one is used to simplify the circuit that determines the next state. ► State diagram ► Next state table ► State reduction ► State assignment (Page 335) rep **Question No: 34** (Marks: 1) - Please choose one The high density FLASH memory cell is implemented using ▶ 1 floating-gate MOS transistor (Page 419) ► 2 floating-gate MOS transistors ► 4 floating-gate MOS transistors ► 6 floating-gate MOS transistors Question No: 35 (Marks: 1) - Please choose one Q2 := Q1 OR X OR Q3 The above ABEL expression will be ► Q2:= Q1 \$ X \$ Q3  $\blacktriangleright$  O2:= O1 # X # O3 (Page 210)  $\blacktriangleright$  Q2:= Q1 & X & Q3  $\blacktriangleright$ Q2:=Q1 ! X ! Q3 Question No: 36 (Marks: 1) - Please choose one Generally, the Power dissipation of \_\_\_\_\_\_ devices remains constant throughout their operation. ►**TTL** (Page 65) ► CMOS 3.5 series ► CMOS 5 Series ▶ Power dissipation of all circuits increases with time. **Ouestion No: 37** (Marks: 1) - Please choose one When the control line in tri-state buffer is high the buffer operates like a gate ► AND ► OR ►NOT (Page 196) ► XOR

► Division

#### Question No: 3 (Marks: 1) - Please choose one

A Karnaugh map is similar to a truth table because it presents all the possible values of input variables and the resulting output of each value.

True rep <u>Click here for Detail</u>

False

#### Question No: 4 (Marks: 1) - Please choose one

The binary numbers A = 1100 and B = 1001 are applied to the inputs of a comparator. What are the output levels?

- ► A > B = 1, A < B = 0, A < B = 1

- ► A > B = 0, A < B = 1, A = B = 0

- A > B = 1, A < B = 0, A = B = 0 (Page 109)

- A > B = 0, A < B = 1, A = B = 1

Question No: 8 (Marks: 1) - Please choose one Flip flops are also called \_ ► Bi-stable dualvibrators ► Bi-stable transformer ▶ Bi-stable multivibrators (Page 228) rep ► Bi-stable singlevibrators **Question No: 9** (Marks: 1) - Please choose one If S=1 and R=0, then Q(t+1) =\_\_\_\_\_\_ for positive edge triggered flip-flop ▶ 0 ▶ 1 (Page 230) ► Invalid Input is invalid Question No: 10 (Marks: 1) - Please choose one If S=1 and R=1, then Q(t+1) =\_\_\_\_\_\_ for negative edge triggered flip-flop ▶ 0 ▶ 1 ► Invalid (Page 230) Input is invalid **Question No: 11** (Marks: 1) - Please choose one The operation of J-K flip-flop is similar to that of the SR flip-flop except that the J-K flip-flop ► Doesn't have an invalid state (Page 232) rep Sets to clear when both J = 0 and K = 0► It does not show transition on change in pulse ► It does not accept asynchronous inputs Question No: 12 (Marks: 1) - Please choose one

The minimum time for which the input signal has to be maintained at the input of flip-flop is called \_\_\_\_\_\_ of the flip-flop.

- ► Set-up time

- ► Hold time (Page 242)

- ▶ Pulse Interval time

- ► Pulse Stability time (PST)

#### Question No: 13 (Marks: 1) - Please choose one

We have a digital circuit. Different parts of circuit operate at different clock frequencies (4MHZ, 2MHZ and 1MHZ), but we have a single clock source having a fix clock frequency (4MHZ), we can get help by

- ► Using S-R Flop-Flop

- ► D-flipflop

- ► J-K flip-flop (Page 252)

- ► T-Flip-Flop

- ► Race condition

- Clock Skew (Page 226) rep

- ► Ripple Effect

- ► None of given options

## Question No: 19 (Marks: 1) - Please choose one

A counter is implemented using three (3) flip-flops, possibly it will have \_\_\_\_\_ maximum output status.

```

Question No: 20 (Marks: 1) - Please choose one

A divide-by-50 counter divides the input ______ signal to a 1 Hz signal.

> 10 Hz

> 50 Hz (Page 298)

> 100 Hz

> 500 Hz

Question No: 21 (Marks: 1) - Please choose one

The design and implementation of synchronous counters start from _____

> Truth table

> k-map

> state table

> state diagram (Page 319)

```

```

Question No: 22 (Marks: 1) - Please choose one

A synchronous decade counter will have _____ flip-flops

```

```

3

4 (Page 281) rep

7

10

```

Question No: 23 (Marks: 1) - Please choose one The output of this circuit is always \_\_\_\_\_.

**Question No: 24 (Marks: 1) - Please choose one** At T0 the value stored in a 4-bit left shift was "1". What will be the value of register after three clock pulses?

2

4

6

8 (not sure) rep

Question No: 27 (Marks: 1) - Please choose one Which is not characteristic of a shift register?

- ► Serial in/parallel in (Page 346)

- Serial in/parallel out

- Parallel in/serial out

- ► Parallel in/parallel out

#### Question No: 28 (Marks: 1) - Please choose one

Assume that a 4-bit serial in/serial out shift register is initially clear. We wish to store the nibble 1100. What will be the 4-bit pattern after the second clock pulse? (Right-most bit first.)

▶ 1100

▶ 00011

▶ 0000

▶ 1111

Click here for detail rep

### Question No: 29 (Marks: 1) - Please choose one

The \_\_\_\_\_\_ of a ROM is the time it takes for the data to appear at the Data Output of the ROM chip after an address is applied at the address input lines

- ► Write Time

- ► Recycle Time

- ► Refresh Time

- ► Access Time (Page 417) rep

**Question No: 30** (Marks: 1) - Please choose one The sequence of states that are implemented by a n-bit Johnson counter is

- n+2 (n plus 2)

2n (n multiplied by 2) (Page 354) rep

2<sup>n</sup> (2 raise to power n)

n<sup>2</sup> (n raise to power 2)

- George Martine G

## FINALTERM EXAMINATION Fall 2009

**Question No: 1** (Marks: 1) - Please choose one NOR Gate can be used to perform the operation of AND, OR and NOT Gate

FALSETRUE (Page 250)

Question No: 2 (Marks: 1) - Please choose one The output of an XNOR gate is 1 when \_\_\_\_\_

- I) All the inputs are zero

- II) Any of the inputs is zero

- III) Any of the inputs is one

- IV) All the inputs are one

- ► I Only

- ► IV Only

- ► I and IV only

- ► II and III only (Page 53)

Question No: 3 (Marks: 1) - Please choose one NAND gate is formed by connecting \_\_\_\_\_

- ► AND Gate and then NOT Gate (Page 45)

- ► NOT Gate and then AND Gate

- ► AND Gate and then OR Gate

- ► OR Gate and then AND Gate

Question No: 4 (Marks: 1) - Please choose one

Consider A=1,B=0,C=1. A, B and C represent the input of three bit NAND gate the output of the NAND gate will be \_\_\_\_\_

- ► Zero

- ▶ One (Page 46)

- ► Undefined

- ► No output as input is invalid

```

Question No: 5 (Marks: 1) - Please choose one

The capability that allows the PLDs to be programmed after they have been installed on a circuit board is called

► Radiation-Erase programming method (REPM)

► In-System Programming (ISP) (Page 194)

► In-chip Programming (ICP)

► Electronically-Erase programming method(EEPM)

Question No: 6 (Marks: 1) - Please choose one

The ABEL symbol for "OR" operation is

▶!

▶ &

▶ # (Page 201) rep

► $

Question No: 7 (Marks: 1) - Please choose one

If S=1 and R=1, then Q(t+1) = ______ for negative edge triggered flip-flop

▶ 0

▶ 1

Invalid (Page 230) rep

▶ Input is invalid

Question No: 8 (Marks: 1) - Please choose one

The operation of J-K flip-flop is similar to that of the SR flip-flop except that the J-K flip-flop

▶ Doesn't have an invalid state (Page 232) rep

Sets to clear when both J = 0 and K = 0

► It does not show transition on change in pulse

It does not accept asynchronous inputs

Question No: 9 (Marks: 1) - Please choose one

For a gated D-Latch if EN=1 and D=1 then Q(t+1) = ____

▶ 0

▶ 1 (Page 227) rep

\blacktriangleright Q(t)

► Invalid

Question No: 10 (Marks: 1) - Please choose one

In asynchronous digital systems all the circuits change their state with respect to a common clock

► True

► False (Page 245) rep

```

### Question No: 22 (Marks: 1) - Please choose one

At T0 the value stored in a 4-bit left shift was "1". What will be the value of register after three clock pulses?

### Question No: 23 (Marks: 1) - Please choose one

A bidirectional 4-bit shift register is storing the nibble 1110. Its RIGHT/LEFT input is LOW. The nibble 0111 is waiting to be entered on the serial data-input line. After two clock pulses, the shift register is storing \_\_\_\_\_\_

- 1110

0111

1000

1001 Clic

- ► 1001 <u>Click he re for detail</u>

### Question No: 24 (Marks: 1) - Please choose one

The high density FLASH memory cell is implemented using \_\_\_\_\_

### ▶ 1 floating-gate MOS transistor (Page 419) rep

- ► 2 floating-gate MOS transistors

- ► 4 floating-gate MOS transistors

- ► 6 floating-gate MOS transistors

## Question No: 25 (Marks: 1) - Please choose one

In order to synchronize two devices that consume and produce data at different rates, we can use \_\_\_\_\_

- Read Only Memory

- Fist In First Out Memory (Page 425)

- ► Flash Memory

- ► Fast Page Access Mode Memory

Muhammad Moaaz Siddiq – MCS (2nd) mc100401285@Gmail.com Campus:- Institute of E-Learning & Modern

Studies (IEMS) Samundari

### Question No: 26 (Marks: 1) - Please choose one

If the FIFO Memory output is already filled with data then \_\_\_\_\_

- ► It is locked; no data is allowed to enter

- ► It is not locked; the new data overwrites the previous data.

- Previous data is swapped out of memory and new data enters

- None of given options

### Question No: 27 (Marks: 1) - Please choose one

The process of converting the analogue signal into a digital representation (code) is known as

- ► Strobing

- ► Amplification

- ► Quantization (Page 445)

- ► Digitization

### Question No: 28 (Marks: 1) - Please choose one

Above is the circuit diagram of \_\_\_\_\_

- ► Asynchronous up-counter (Page 270) rep

- Asynchronous down-counter

- ► Synchronous up-counter

- Synchronous down-counter

### Question No: 29 (Marks: 1) - Please choose one

$(A+B)(A+\overline{B}+C)(\overline{A}+C)$

is an example of \_

- Product of sum form (Page 77)

- Sum of product form

- Demorgans law

- ► Associative law

#### Question No: 30 (Marks: 1) - Please choose one Q2 :=Q1 OR X OR Q3

The above ABEL expression will be

- $\blacktriangleright$  Q2:= Q1 \$ X \$ Q3

- ► Q2:= Q1 # X # Q3 (Page 210)

- ► Q2:= Q1 & X & Q3

- $\blacktriangleright$  Q2:= Q1 ! X ! Q3

### FINALTERM EXAMINATION Fall 2009

Question No: 1 (Marks: 1) - Please choose one Caveman number system is Base \_\_\_\_\_ number system

► I Only

► IV Only

► I and IV only (Page 53)

► II and III only

Question No: 3 (Marks: 1) - Please choose one

The decimal "17" in BCD will be represented as \_\_\_\_\_10001(right opt is not given)

11101

11011

10111 (According to rule) rep

11110

### Question No: 4 (Marks: 1) - Please choose one

A Karnaugh map is similar to a truth table because it presents all the possible values of input variables and the resulting output of each value.

True <u>Click here for Detail</u> rep

False

Question No: 5 (Marks: 1) - Please choose one The simplest and most commonly used Decoders are the \_\_\_\_\_ Decoders

n to 2n (Page 158)

(n-1) to 2n

(n-1) to (2n-1)

n to 2n-1

## Question No: 6 (Marks: 1) - Please choose one

The \_\_\_\_\_ Encoder is used as a keypad encoder.

- ► 2-to-8 encoder

- ► 4-to-16 encoder

- ► BCD-to-Decimal

- **Decimal-to-BCD Priority** (Page 166)

### Question No: 7 (Marks: 1) - Please choose one

3-to-8 decoder can be used to implement Standard SOP and POS Boolean expressions

► True (Page 161)

► False

### Question No: 8 (Marks: 1) - Please choose one

If S=1 and R=0, then Q(t+1) =\_\_\_\_\_\_ for positive edge triggered flip-flop

- ▶ 0

- ▶ 1 (Page 230)

- ► Invalid

- ► Input is invalid

### Question No: 9 (Marks: 1) - Please choose one

If the S and R inputs of the gated S-R latch are connected together using a \_\_\_\_\_\_gate then there is only a single input to the latch. The input is represented by D instead of S or R (A gated D-Latch)

- ► AND

- ► OR

- ▶ NOT (Page 226)

- ► XOR

### Question No: 10 (Marks: 1) - Please choose one

In asynchronous digital systems all the circuits change their state with respect to a common clock

- ► True

- ► False (Page 245) rep

### Question No: 11 (Marks: 1) - Please choose one

The low to high or high to low transition of the clock is considered to be a(n)

- ► State

- **Edge** (Page 228)

- ► Trigger

- ► One-shot

### Question No: 12 (Marks: 1) - Please choose one

A positive edge-triggered flip-flop changes its state when

### ► Low-to-high transition of clock (Page 228)

- ► High-to-low transition of clock

- ► Enable input (EN) is set

- Preset input (PRE) is set

### Question No: 13 (Marks: 1) - Please choose one

RCO Stands for

- Reconfiguration Counter Output

- Reconfiguration Clock Output

- ► Ripple Counter Output

- ► Ripple Clock Output (Page 285)

### Question No: 14 (Marks: 1) - Please choose one

Bi-stable devices remain in either of their \_\_\_\_\_\_ states unless the inputs force the device to switch its state

- ► Ten

- ► Eight

- ► Three

- Two (Page 262) rep

### Question No: 15 (Marks: 1) - Please choose one

\_ is one of the examples of asynchronous inputs.

- ► J-K input

- S-R input

- ► D input

- Clear Input (CLR) (Page 255) rep

### Question No: 16 (Marks: 1) - Please choose one

\_\_\_\_\_occurs when the same clock signal arrives at different times at different clock inputs due to propagation delay.

- ► Race condition

- Clock Skew (Page 226) rep

- ► Ripple Effect

- None of given options

### Question No: 17 (Marks: 1) - Please choose one

A transparent mode means \_\_\_\_

### ▶ The changes in the data at the inputs of the latch are seen at the output (Page 245)

- ► The changes in the data at the inputs of the latch are not seen at the output

- ▶ Propagation Delay is zero (Output is immediately changed when clock signal is applied)

- ▶ Input Hold time is zero (no need to maintain input after clock transition)

## **Ouestion No: 18 (Marks: 1) - Please choose one** In \_\_\_\_\_ outputs depend only on the current state. ► Mealy machine ► Moore Machine (Page 332) State Reduction table State Assignment table Question No: 19 (Marks: 1) - Please choose one The alternate solution for a multiplexer and a register circuit is Parallel in / Serial out shift register (Page 356) rep Serial in / Parallel out shift register ► Parallel in / Parallel out shift register Serial in / Serial Out shift register Ouestion No: 20 (Marks: 1) - Please choose one The alternate solution for a demultiplexer-register combination circuit is Parallel in / Serial out shift register Serial in / Parallel out shift register (Page 356) rep ► Parallel in / Parallel out shift register Serial in / Serial Out shift register Ouestion No: 21 (Marks: 1) - Please choose one In asynchronous transmission when the transmission line is idle, ► It is set to logic low ▶ It is set to logic high (Page 356) rep Remains in previous state ► State of transmission line is not used to start transmission Question No: 22 (Marks: 1) - Please choose one Smallest unit of binary data is a **Bit** (Page 394) ► Nibble ► Byte ► Word Question No: 23 (Marks: 1) - Please choose one A Nibble consists of bits ▶ 2 ▶ 4 (Page 394) rep ▶ 8 ▶ 16

## Question No: 24 (Marks: 1) - Please choose one A GAL is essentially a .

- Non-reprogrammable PAL

- ► PAL that is programmed only by the manufacturer

- ► Very large PAL

- ► Reprogrammable PAL (Page 183) rep

### Question No: 25 (Marks: 1) - Please choose one

A 8-bit serial in / parallel out shift register contains the value "8", \_\_\_\_\_ clock signal(s) will be required to shift the value completely out of the register.

1

2

4

8 (Page 356) rep

Question No: 26 ( Marks: 1 ) - Please choose one DRAM stands for \_\_\_\_\_

- **Dynamic RAM** (Page 407) rep

- Data RAM

- Demoduler RAM

- None of given options

Question No: 27 (Marks: 1) - Please choose one FIFO is an acronym for \_\_\_\_\_

### First In, First Out (Page 424) rep

- ► Fly in, Fly Out

- ► Fast in, Fast Out

- None of given options

### Question No: 28 (Marks: 1) - Please choose one

## (Diagram is missing)

In the circuit diagram of 3-bit synchronous counter shown above, The red rectangle would be replaced by which gate?

- ► AND

- ► OR

- ► NAND

- ► XNOR

**Question No: 29 (Marks: 1) - Please choose one** The sequence of states that are implemented by a n-bit Johnson counter is

- ▶ n+2 (n plus 2)

- 2n (n multiplied by 2) (Page 354) rep

- $\blacktriangleright$  2n (2 raise to power n)

- $\blacktriangleright$  n2 (n raise to power 2)

# Question No: 30 (Marks: 1) - Please choose one Stack is an acronym for \_\_\_\_\_

- ► FIFO memory

- ► LIFO memory (Page 429) rep

- ► Flash Memory

- Bust Flash Memory

### FINALTERM EXAMINATION Fall 2009

### **Question No: 1 ( Marks: 1 ) - Please choose one** The diagram given below represents \_\_\_\_\_

**Question No: 2 ( Marks: 1 ) - Please choose one** Excess-8 code assigns \_\_\_\_\_\_ to "+7"

### ▶ 0000 (Page 34) rep

- ▶ 1001

- ▶ 1000

- ▶ 1111

### **Question No: 3 (Marks: 1) - Please choose one** NOR gate is formed by connecting

### ► OR Gate and then NOT Gate (Page 47)

- ► NOT Gate and then OR Gate

- ► AND Gate and then OR Gate

- ► OR Gate and then AND Gate

### Question No: 4 (Marks: 1) - Please choose one

A full-adder has a Cin = 0. What are the sum ( $\langle PRIVATE "TYPE=PICT; ALT=sigma" \rangle$ ) and the carry (Cout) when A = 1 and B = 1?

- $\blacktriangleright = 0$ , Cout = 0

- ▶ = 0, Cout = 1 (Page 135)

- $\blacktriangleright = 1$ , Cout = 0

- $\blacktriangleright = 1$ , Cout = 1

Question No: 5 (Marks: 1) - Please choose one

rep

A particular half adder has

- ► 2 INPUTS AND 1 OUTPUT

- ► 2 INPUTS AND 2 OUTPUT (Page 134)

- ► 3 INPUTS AND 1 OUTPUT

- ► 3 INPUTS AND 2 OUTPUT

### Question No: 6 (Marks: 1) - Please choose one

THE FOUR OUTPUTS OF TWO 4-INPUT MULTIPLEXERS, CONNECTED TO FORM A 16-INPUT MULTIPLEXER, ARE CONNECTED TOGETHER THROUGH A 4-INPUT \_\_\_\_\_\_ GATE

- ► AND

- **OR** (Page 171)

- ► NAND

- ► XOR

### Question No: 7 (Marks: 1) - Please choose one

A FIELD-PROGRAMMABLE LOGIC ARRAY CAN BE PROGRAMMED BY THE USER AND NOT BY THE MANUFACTURER.

TRUE (Page 182)

FALSE

### Question No: 8 ( Marks: 1 ) - Please choose one Flip flops are also called \_\_\_\_\_

- Bi-stable dualvibrators

- ► Bi-stable transformer

- ► Bi-stable multivibrators (Page 228)

- Bi-stable singlevibrators

### Question No: 9 (Marks: 1) - Please choose one

A positive edge-triggered flip-flop changes its state when \_\_\_\_\_

- Low-to-high transition of clock (Page 228)

- High-to-low transition of clock

- ► Enable input (EN) is set

- Preset input (PRE) is set

## Question No: 10 (Marks: 1) - Please choose one

\_ is one of the examples of synchronous inputs.

## ► J-K input (Page 235)

- ► EN input

- Preset input (PRE)

- ► Clear Input (CLR)

## Question No: 11 (Marks: 1) - Please choose one

THE GLITCHES DUE TO RACE CONDITION CAN BE AVOIDED BY USING A

- ► GATED FLIP-FLOPS

- ► PULSE TRIGGERED FLIP-FLOPS

- ► POSITIVE-EDGE TRIGGERED FLIP-FLOPS

## ► NEGATIVE-EDGE TRIGGERED FLIP-FLOPS (Page 267) rep

### Question No: 12 (Marks: 1) - Please choose one

The design and implementation of synchronous counters start from \_\_\_\_\_

- ► Truth table

- ► k-map

- ► state table

- ► state diagram (Page 319) rep

Question No: 13 (Marks: 1) - Please choose one THE HOURS COUNTER IS IMPLEMENTED USING \_\_\_\_\_

- ► ONLY A SINGLE MOD-12 COUNTER IS REQUIRED

- MOD-10 AND MOD-6 COUNTERS

- ► MOD-10 AND MOD-2 COUNTERS

- ► A SINGLE DECADE COUNTER AND A FLIP-FLOP (Page 299) rep

### Question No: 14 (Marks: 1) - Please choose one

Given the state diagram of an up/down counter, we can find \_

## ► The next state of a given present state (Page 371) rep

- ► The previous state of a given present state

- ▶ Both the next and previous states of a given state

- ► The state diagram shows only the inputs/outputs of a given states

## Muhammad Moaaz Siddiq – MCS (2nd)

mc100401285@Gmail.com

Campus:- Institute of E-Learning & Modern Studies (IEMS) Samundari

Question No: 21 (Marks: 1) - Please choose one 5-BIT JOHNSON COUNTER SEQUENCES THROUGH \_\_\_\_\_ STATES ▶ 7 ▶ 10 (Page 354) rep ▶ 32 ▶ 25 Question No: 22 (Marks: 1) - Please choose one Q output of the last flip-flop of the shift register is connected to the data input of the first In flip-flop of the shift register. ► Moore machine ► Meally machine ► Johnson counter ► Ring counter (Page 355) Question No: 23 (Marks: 1) - Please choose one **DRAM** stands for ► Dynamic RAM (Page 407) rep ► Data RAM ► Demoduler RAM None of given options Question No: 24 (Marks: 1) - Please choose one If the FIFO Memory output is already filled with data then \_\_\_\_\_ ▶ It is locked: no data is allowed to enter ▶ It is not locked; the new data overwrites the previous data. ▶ Previous data is swapped out of memory and new data enters None of given options Question No: 25 (Marks: 1) - Please choose one LUT is acronym for \_\_\_\_\_ Look Up Table (Page 439) rep ► Local User Terminal ► Least Upper Time Period ► None of given options Question No: 26 (Marks: 1) - Please choose one of a D/A converter is determined by comparing the actual output of a D/A converter with the expected output. ► Resolution ► Accuracy (Page 460) rep

- Accuracy (Page 400)

- QuantizationMissing Code

| Question No: 27 (Marks: 1) - Please choose one             | (Diagram is missing)                           |

|------------------------------------------------------------|------------------------------------------------|

| In the circuit diagram of 3-bit synchronous counterThe red | rectangle, shown above would be replaced which |

| gate?                                                      |                                                |

- ► AND

- ► OR

- ► NAND

- ► XNOR

Question No: 28 (Marks: 1) - Please choose one WHEN BOTH THE INPUTS OF EDGE-TRIGGERED J-K FLOP-FLOP ARE SET TO LOGIC ZERO ------

- ► THE FLOP-FLOP IS TRIGGERED

- ► Q=0 AND Q'=1

- ▶ Q=1 AND Q'=0

- ► THE OUTPUT OF FLIP-FLOP REMAINS UNCHANGED (page 223)

Question No: 29 (Marks: 1) - Please choose one

A frequency counter \_

- Counts pulse width

- Counts no. of clock pulses in 1 second (Page 301) rep

- ► Counts high and low range of given clock pulse

- ► None of given options

Question No: 30 (Marks: 1) - Please choose one Stack is an acronym for \_\_\_\_\_

- ► FIFO memory

- ► LIFO memory (Page 429) rep

- ► Flash Memory

- Bust Flash Memory