### **Lecture Handouts**

# **Computer Architecture**

# **Appendix**

# **Reading Material**

Handouts

# **Summary**

- 1. Introduction to FALSIM

- 2. Preparing source files for FALSIM

- 3. Using FALSIM

- 4. FALCON-A assembly language techniques

### **FALSIM**

### 1. Introduction to FALSIM:

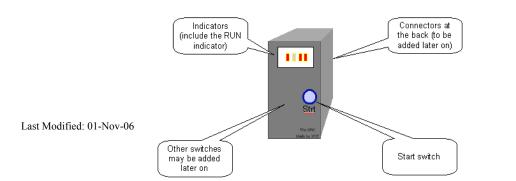

FALSIM is the name of the software application which consists of the FALCON-A assembler and the FALCON-A simulator. It runs under Windows XP.

### **FALCON-A Assembler:**

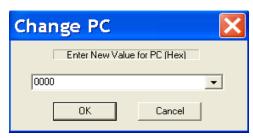

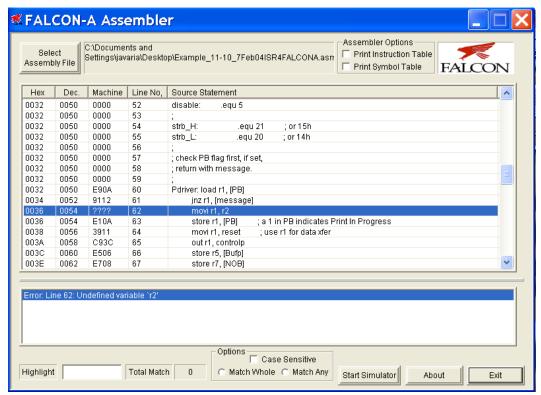

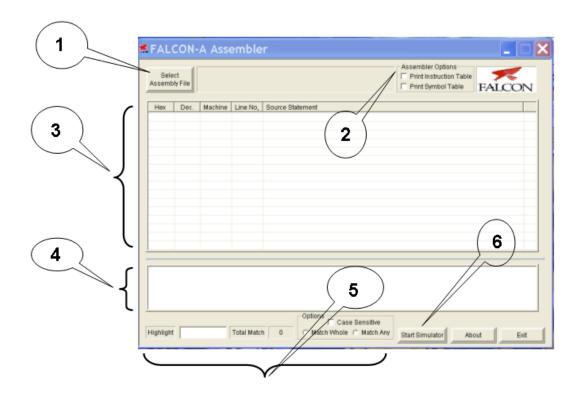

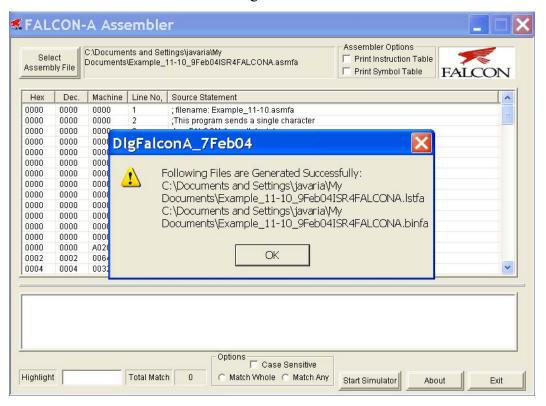

Figure 1 shows a snapshot of the FALCON-A Assembler. This tool loads a FALCON-A assembly file with a (.asmfa) extension and parses it. It shows the parse results in an error log, lets the user view the assembled file's contents in the file listing and also provides the features of printing the machine code, an Instruction Table and a Symbol Table to a FALCON-A listing file. It also allows the user to run the FALCON-A Simulator.

The FALCON-A Assembler has two main modules, the 1st-pass and the 2nd-pass. The 1st-pass module takes an assembly file with a (.asmfa) extension and processes the file contents. It then creates a Symbol Table

which corresponds to the storage of all program variables, labels and data values in a data structure at the implementation level. If the 1st-pass completes successfully a Symbol Table is produced as an output, which is used by the 2nd-pass module. Failures of the 1st-pass are handled by the assembler using its exception handling mechanism.

The 2nd-pass module sequentially processes the .asmfa file to interpret the instruction opcodes, register opcodes and constants using the symbol table. It then produces a list file with a .lstfa extension independent of successful or failed pass. If the pass is successful a binary file with a .binfa extension is produced which contains the machine code for the program in the assembly file.

### **FALCON-A Simulator**:

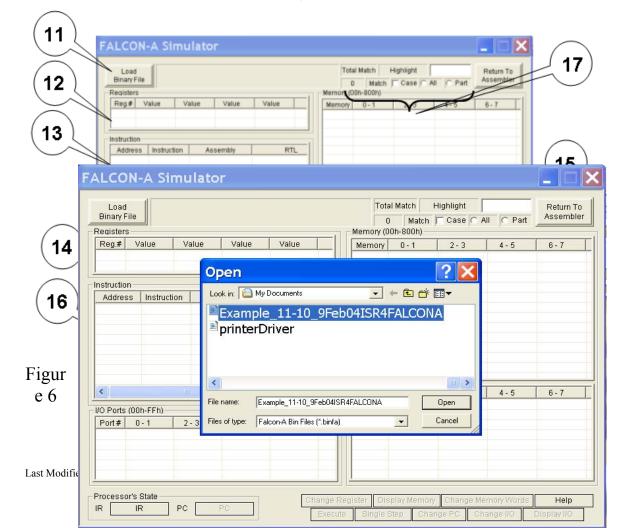

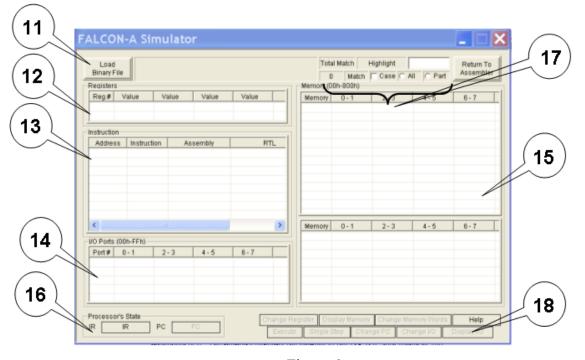

Figure 6 shows a snapshot of the FALCON-A Simulator. This tool loads a FALCON-A binary file with a (.binfa) extension and presents its contents into different areas of the simulator. It allows the user to execute the program to a specific point within a time frame or just executes it, line by line. It also allows the user to view the registers, I/O port values and memory contents as the instructions execute.

### **FALSIM Features**:

The FALCON-A Assembler provides its user with the following features:

Select Assembly File: Labeled as "1" in Figure 1, this feature enables the user to choose a FALCON-A assembly file and open it for processing by the assembler.

Assembler Options: Labeled as "2" in Figure 1.

### • Print Symbol Table

This feature if selected writes the Symbol Table (produced after the execution of the 1st-pass of the assembler) to a FALCON-A list file with an extension of (.lstfa). The Symbol Table includes data members, data addresses and labels with their respective values.

#### • Print Instruction Table

This feature if selected writes the Instruction Table to a FALCON-A list file with an extension of (.lstfa).

List File: Labeled as "3", in Figure 1, the List File feature gives a detailed insight of the FALCON-A listing file, which is produced as a result of the execution of the 1st and 2nd-pass. It shows the Program Counter value in hexadecimal and decimal formats along with the machine code generated for every line of assembly code. These values are printed when the 2nd-pass is completed.

*Error Log:* The Error Log is labeled as "4" in Figure 1. It informs the user about the errors and their respective details, which occurs in any of the passes of the assembler.

Search: Search is labeled as "5" in Figure 1 and helps the user to search for a certain input with the options of searching with "match whole" and "match any" parts of the string. The search also has the option of checking with/without considering "case-sensitivity". It searches the List File area and highlights the search results using the yellow color. It also indicates the total number of matches found.

Start Simulator: This feature is labeled as "6" in Figure 1. The FALCON-A Simulator is run using the FALCON-A Assembler's Start Simulator option. The FALCON-A Simulator is invoked by the user from the FALCON-A Assembler. Its features are detailed as follows:

Load Binary File: The button labeled as "11" in Figure 6, allows the user to choose and open a FALCON-A binary file with a (.binfa) extension. When a file is being loaded into the simulator all the register, constants (if any) and memory values are set.

Registers: The area labeled as "12" in Figure 6. enables, the user to see values present in different registers before during and after execution.

*Instruction:* This area is labeled as "13" in Figure 6 and contains the value of PC, address of an instruction, its representation in Assembly, the Register Transfer Language, the op-code and the instruction type.

*I/O Ports:* I/O ports are labeled as "14" in Figure 6. These ports are available for the user to enter input operation values and visualize output operation values whenever an I/O operation takes place in the program. The input value for an input operation is given by the user before an instruction executes. The output values are visible in the I/O port area once the instruction has successfully executed.

*Memory:* The memory is divided into 2 areas and is labeled as "15" in Figure 6, to facilitate the view of data stored at different memory locations before, during and after program execution.

*Processor's State:* Labeled as "16" in Figure 6, this area shows the current values of the Instruction register and the Program Counter while the program executes.

Search: The search option for the FALCON-A simulator is labeled as "17" in Figure 6. This feature is similar to the way the search feature of the FALCON-A Assembler works. It offers to highlight the search string which goes as an input, with the "All " and " Part " option. The results of the search are highlighted in the color yellow. It also indicates the total number of matches.

The following is a description of the options available on the button panel labeled as "18" in Figure 6.

Single Step: "Single Step" lets the user execute the program, one instruction at a time. The next instruction is not executed unless the user does a "single step" again. By default, the instruction to be executed will be the one next in the sequence. It changes if the user specifies a different PC value using the Change PC option (explained below).

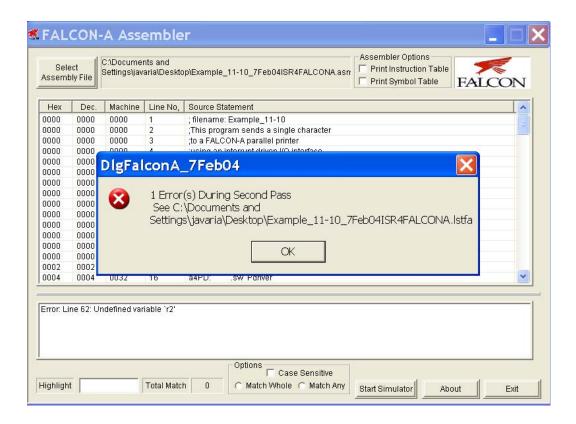

Change PC: This option lets the user change the value of PC (Program Counter). By changing the PC the user can execute the instruction to which the specified PC points.

Execute: By choosing this button the user is able to execute the instructions with the options of execution with/without breakpoint insertion (refer to Fig. 5). In case of breakpoint insertion, the user has the option to choose from a list of valid breakpoint values. It also has the option to set a limit on the time for execution. This "Max Execution Time" option restricts the program execution to a time frame specified by the user, and helps the simulator in exception handling.

Change Register: Using the Change Register feature, the user can change the value present in a particular register.

Change Memory Word: This feature enables the user to change values present at a particular memory location.

Display Memory: Display Memory shows an updated memory area, after a particular memory location other than the pre-existing ones is specified by the user.

Change I/O: Allows the user to give an I/O port value if the instruction to be executed requires an I/O operation. Giving in the input in any one of the I/O ports areas before instruction execution, indicates that a particular I/O operation will be a part of the program and it will have an input from some source. The value given by the user indicates the input type and source.

Display I/O: Display I/O works in a manner similar to Display Memory. Here the user specifies the starting index of an I/O port. This features displays the I/O ports stating from the index specified.

### 2. Preparing source files for FALSIM:

In order to use the FALCON-A assembler and simulator, FALSIM, the source file containing assembly language statements and directives should be prepared according to the following guidelines:

- The source file should contain ASCII text only. Each line should be terminated by a carriage return. The extension .asmfa should be used with each file name. After assembly, a list file with the original filename and an extension .lstfa, and a binary file with an extension .binfa will be generated by FALSIM.

- Comments are indicated by a semicolon (;) and can be placed anywhere in the source file. The FALSIM assembler ignores any text after the semicolon.

- Names in the source file can be of one of the following types:

- Variables: These are defined using the .equ directive. A value must also be assigned to variables when they are defined.

- Addresses in the "data and pointer area" within the memory: These can be defined using the .dw or the .sw directive. The difference between these two directives is that when .dw is used, it is not possible to store any value in the memory. The integer after .dw identifies the number of memory words to be reserved starting at the current address. (The directive .db can be used to reserve bytes in

memory.) Using the .sw directive, it is possible to store a constant or the value of a name in the memory. It is also possible to use pointers with this directive to specify addresses larger than 127. Data tables and jump tables can also be set up in the memory using this directive.

- Labels: An assembly language statement can have a unique label associated with it. Two assembly language statements cannot have the same name. Every label should have a colon (:) after it.

- Use the .org 0 directive as the first line in the program. Although the use of this line is optional, its use will make sure that FALSIM will start simulation by picking up the first instruction stored at address 0 of the memory. (Address 0 is called the reset address of the processor). A jump [first] instruction can be placed at address 0, so that control is transferred to the first executable statement of the main program. Thus, the label first serves as the identifier of the "entry point" in the source file. The .org directive can also be used anywhere in the source file to force code at a particular address in the memory.

- Address 2 in the memory is reserved for the pointer to the Interrupt Service Routine (ISR). The .sw directive can be used to store the address of the first instruction in the ISR at this location.

- Address 4 to 125 can be used for addresses of data and pointers<sup>1</sup>. However, the main program must start at address 126 or less<sup>2</sup>, otherwise FALSIM will generate an error at the **jump [first]** instruction.

- The main program should be followed by any subprograms or procedures. Each procedure should be terminated with a **ret** instruction. The ISR, if any, should be placed after the procedures and should be terminated with the **iret** instruction.

- The last line in the source file should be the **.end** directive.

- The .equ directive can be used anywhere in the source file to assign values to variables.

- It is the responsibility of the programmer to make sure that code does not overwrite data when the assembly process is performed, or vice versa. As an example, this can happen if care is not exercised during the use of the .org directive in the source file.

## 3. Using FALSIM:

Last Modified: 01-Nov-06 Page 6

\_

<sup>&</sup>lt;sup>1</sup> Any address between 4 and 14 can be used in place of the displacement field in load or store instructions. Recall that the displacement field is just 5 bits in the instruction word.

<sup>&</sup>lt;sup>2</sup> This restriction is because of the face that the immediate operand in the **movi** instruction must fit an 8-bit field in the instruction word.

- To start FALSIM (the FALCON-A assembler and simulator), double click on the FALSIM icon. This will display the assembler window, as shown in the Figure 1.

- Select one or both assembler options shown on the top right corner of the assembler window labeled as "2". If no option is selected, the symbol table and the instruction table will not be generated in the list (.lstfa) file.

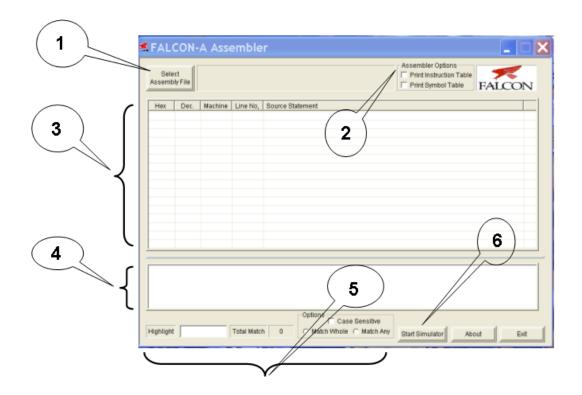

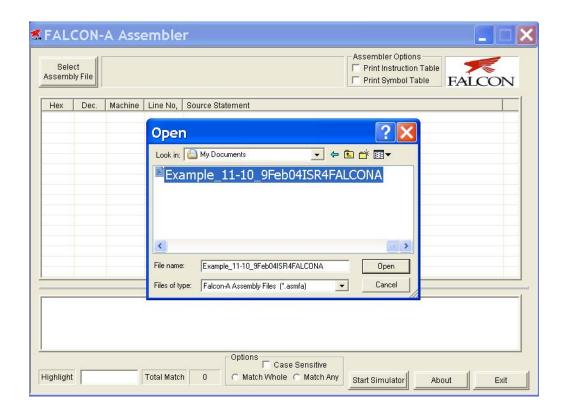

- Click on the select assembly file button labeled as "1". This will open the dialog box as shown in the Figure 2.

- Select the path and file containing the source program that is to be assembled.

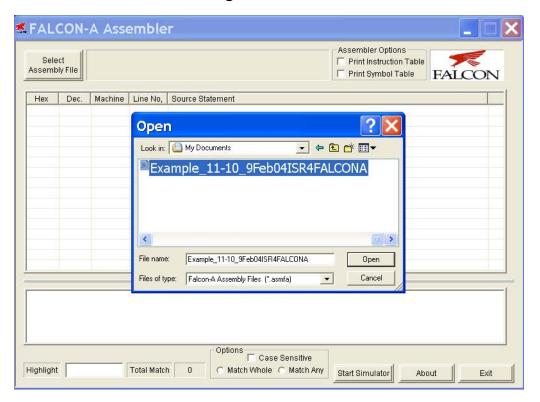

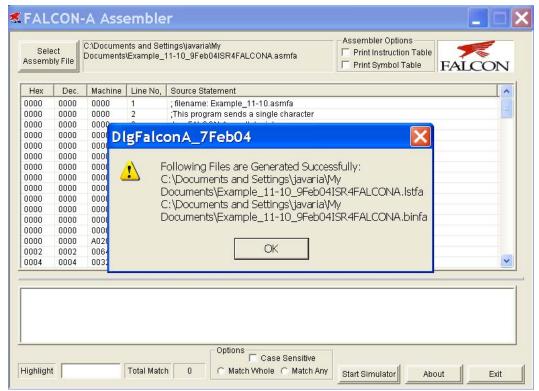

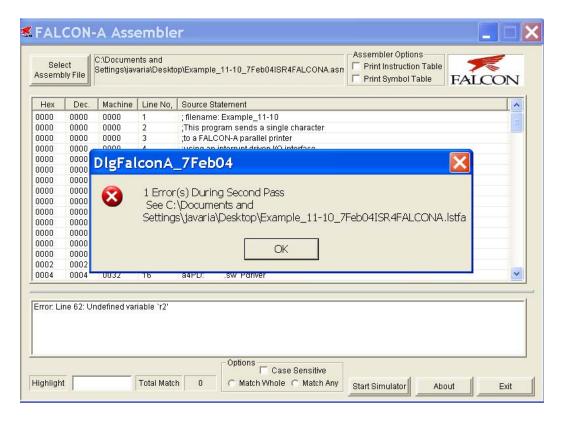

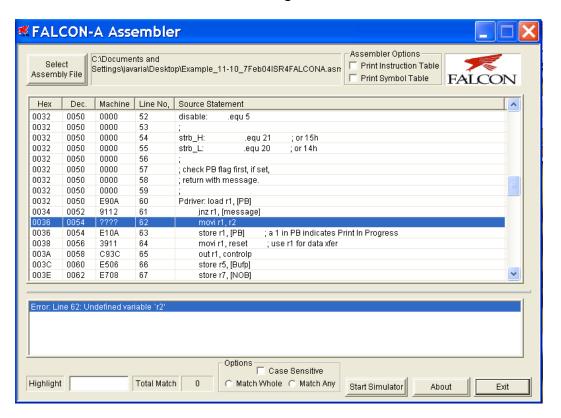

- Click on the open button. FALSIM will assemble the program and generate two files with the same filename, but with different extensions. A list file will be generated with an extension .lstfa, and a binary (executable) file will be generated with an extension .binfa. FALSIM will also display the list file and any error messages in two separate panes, as shown in Figure 3.

- Double clicking on any error message highlights and displays the corresponding erroneous line in the program listing window pane for the user. This is shown in Figure 4. The highlight feature can also be used to display any text string, including statements with errors in them. If the assembler reported any errors in the source file, then these errors should be corrected and the program should be assembled again before simulation can be done. Additionally, if the source file had been assembled correctly at an earlier occasion, and a correct binary (.binfa) file exists, the simulator can be started directly without performing the assembly process.

- To start the simulator, click on the start simulation button labeled as "6". This will open the dialog box shown in Figure 6.

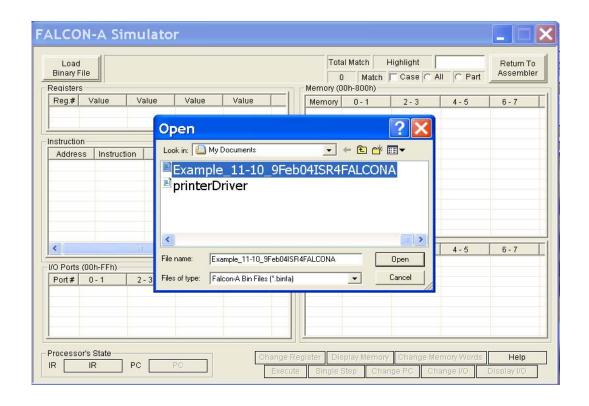

- Select the binary file to be simulated, and click open as shown in Figure 7.

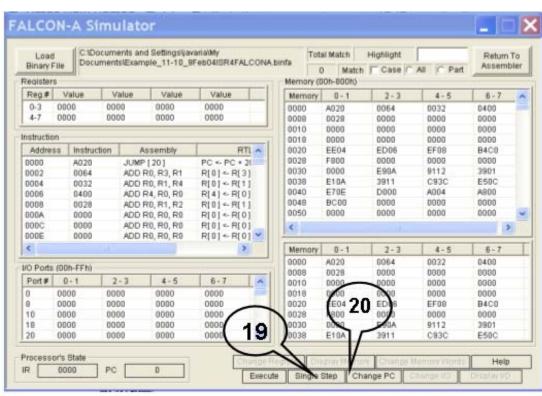

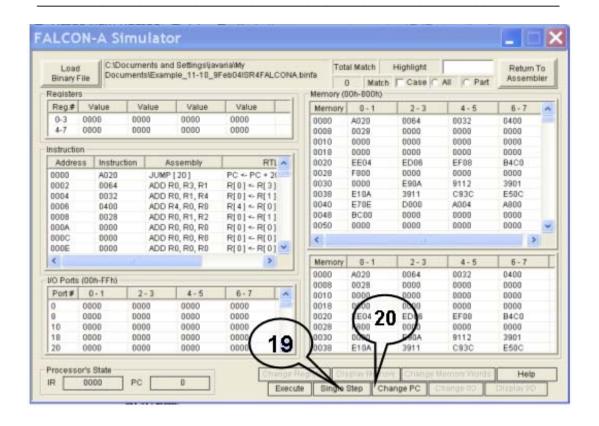

- This will open the simulation window with the executable program loaded in it as shown in Figure 8. The details of the different panes in

this window were given in section 1 earlier. Notice that the first instruction at address 0 is ready for execution. All registers—are initialized to 0. The memory contains the address of the ISR (i.e., 64h which is 100 decimal) at location 2 and the address of the printer driver at location 4. These two addresses are determined at assembly time in our case. In a real situation, these addresses will be determined at execution time by the operating system, and thus the ISR and the printer driver will be located in the memory by the operating system (called re-locatable code). Subsequent memory locations contain constants defined in the program.

- Click single step button labeled as "19". FALSIM will execute the **jump [main]** instruction at address 0 and the PC will change to 20h (32 decimal), which is the address of the first instruction in the main program (i.e., the value of main).

- Although in a real situation, there will be many instructions in the main program, those instructions are not present in the dummy calling program. The first useful instruction is shown next. It loads the address of the printer driver in r6 from the pointer area in the memory. The registers r5 and r7 are also set up for passing the starting address of the print buffer and the number of bytes to be printed. In our dummy program, we bring these values in to these registers from the data area in the memory, and then pass these values to the printer driver using these two registers. Clicking on the single step button twice, executes these two instructions.

- The execution of the call instruction simulates the event of a print request by the user. This transfers control to the printer driver. Thus, when the **call r4**, **r6** instruction is single stepped, the PC changes to 32h (50 decimal) for executing the first instruction in the printer driver.

- Double click on memory location 000A, which is being used for holding the PB (printer busy) flag. Enter a 1 and click the change memory button. This will store a 0001 in this location, indicating that a previous print job is in progress. Now click single step and note that this value is brought from memory location 000E into register r1. Clicking single step again will cause the jnz r1, [message] instruction to execute, and control will transfer to the message routine at address 0046h. The nop instruction is used here as a place holder.

- Click again on the single step button. Note that when the **ret r4** instruction executes, the value in r4 (i.e., 28h) is brought into the PC. The blue highlight bar is placed on the next instruction after the **call r4**, **r6** instruction in the main program. In case of the dummy calling program, this is the **halt** instruction.

- Double click on the value of the PC labeled as "20". This will open a

- dialog box shown below. Enter a value of the PC (i.e., 26h) corresponding to the **call r4, r6** instruction, so that it can be executed again. A "list" of possible PC values can also be pulled down using, and 0026h can be selected from there as well.

- Click single step again to enter the printer driver again.

- Change memory location 000A to a 0, and then single step the first instruction in the printer driver. This will bring a 0 in r1, so that when the next jnz r1, [message] instruction is executed, the branch will not be taken and control will transfer to the next instruction after this instruction. This is mivi r1, 1 at address 0036h.

- Continue single stepping.

- Notice that a 1 has been stored in memory location 000A, and r1 contains 11h, which is then transferred to the output port at address 3Ch (60 decimal) when the **out r1, controlp** instruction executes. This can be verified by double clicking on the top left corner of the I/O port pane, and changing the address to 3Ch. Another way to display the value of an I/O port is to scroll the I/O window pane to the desired position.

- Continue single stepping till the **int** instruction and note the changes in different panes of the simulation window at each step.

- When the **int** instruction executes, the PC changes to 64h, which is the address of the first instruction in the ISR. Clicking single step executes this instruction, and loads the address of **temp** (i.e., 0010h) which is a

temporary memory area for storing the environment. The five **store** instructions in the ISR save the CPU environment (working registers) before the ISR change them.

- Single step through the ISR while noting the effects on various registers, memory locations, and I/O ports till the **iret** instruction executes. This will pass control back to the printer driver by changing the PC to the address of the **jump [finish]** instruction, which is the next instruction after the **int** instruction

- Double click on the value of the PC. Change it to point to the **int** instruction and click single step to execute it again. Continue to single step till the **in r1**, **statusp** instruction is ready for execution.

- Change the I/O port at address 3Ah (which represents the status port at address 58) to 80 and then single step the **in r1**, **statusp** instruction. The value in r1 should be 0080.

- Single step twice and notice that control is transferred to the **movi r7**, **FFFF**<sup>3</sup> instruction, which stores an error code of -1 in r1.

Last Modified: 01-Nov-06 Page 10

\_

<sup>&</sup>lt;sup>3</sup> The instruction was originally **movi r7, -1.** Since it was converted to machine language by the assembler, and then reverse assembled by the simulator, it became **movi r7, FFFF.** This is because the machine code stores the number in 16-bits after sign-extension. The result will be the same in both cases.

Figure 1

Figure 2

Figure 3

Figure 4

Figure 5

Figure 7

Figure 8

### 4. FALCON-A assembly language programming techniques:

- If a signed value, x, cannot fit in 5 bits (i.e., it is outside the range -16 to +15), FALSIM will report an error with a **load r1**, [x] or a **store r1**, [x] instruction. To overcome this problem, use **movi r2**, x followed by **load r1**, [r2].

- If a signed value, x, cannot fit in 8 bits (i.e., it is outside the range 128 to +127), even the previous scheme will not work. FALSIM will report an error with the **movi r2**, x instruction. The following instruction sequence should be used to overcome this limitation of the FALCON-A. First store the 16-bit address in the memory using the .sw directive. Then use two load instructions as shown below:

```

a: .sw x

load r2, [a]

load r1, [r2]

```

This is essentially a "memory-register-indirect" addressing. It has been made possible by the .sw directive. The value of a should be less than 15.

- A similar technique can be used with immediate ALU instructions for large values of the immediate data, and with the transfer of control (call and jump) instructions for large values of the target address.

- Large values (16-bit values) can also be stored in registers using the **mul** instruction combined with the **addi** instruction. The following instructions bring a 201 in register r1.

```

movi r2, 10

movi r3, 20

mul r1, r2, r3 ; r1 contains 200 after this instruction

addi r1, r1, 1 ; r1 now contains 201

```

- Moving from one register to another can be done by using the instruction addi r2, r1, 0.

- Bit setting and clearing can be done using the logical (and, or, not, etc) instructions.

- Using shift instructions (shiftl, asr, etc.) is faster that **mul** and **div**, if the multiplier or divisor is a power of 2.

### **Lecture Handout**

## **Computer Architecture**

### Lecture No. 1

Reading Material

Vincent P. Heuring & Harry F. Jordan Computer Systems Design and Architecture Chapter 1 1.1, 1.2, 1.3, 1.4, 1.5

### **Summary**

- 1) Distinction between computer architecture, organization and design

- 2) Levels of abstraction in digital design

- 3) Introduction to the course topics

- 4) Perspectives of different people about computers

- 5) General operation of a stored program digital computer

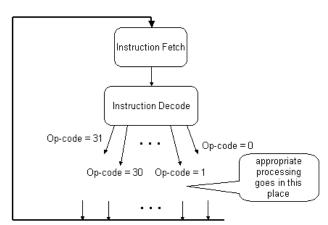

- 6) The Fetch-Execute process

- 7) Concept of an ISA(Instruction Set Architecture)

#### Introduction

This course is about Computer Architecture. We start by explaining a few key terms.

### The General Purpose Digital Computer

How can we define a 'computer'? There are several kinds of devices that can be termed "computers": from desktop machines to the microcontrollers used in appliances such as a microwave oven, from the Abacus to the cluster of tiny chips used in parallel processors, etc. For the purpose of this course, we will use the following definition of a computer:

"an electronic device, operating under the control of instructions stored in its own memory unit, that can accept data (input), process data arithmetically and logically, produce output from the processing, and store the results for future use." [1]

Thus, when we use the term computer, we actually mean a digital computer. There are many digital computers, which have dedicated purposes, for example, a computer used in an automobile that controls the spark

Notion of a System

timing for the engine. This means that when we use the term computer, we actually mean a general-purpose digital computer that can perform a variety of arithmetic and logic tasks.

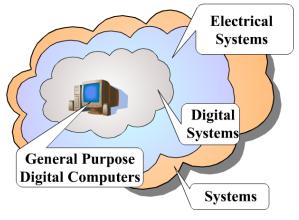

### The Computer as a System

Now we examine the notion of a system, and the place of digital computers in the general universal set of systems. A "system" is a collection of elements, or components, working together on one or more inputs to produce one or more desired outputs.

There are many types of systems in the world. Examples include:

- Chemical systems

- Optical systems

- Biological systems

- Electrical systems

- Mechanical systems, etc.

These are all subsets of the general universal set of "systems". One particular subset of interest is an "electrical system". In case of electrical systems, the inputs as well as the outputs are electrical quantities, namely voltage and current. "Digital systems" are a subset of electrical systems. The inputs and outputs are digital quantities in this case. General-purpose digital computers are a subset of digital systems. We will focus on general-purpose digital computers in this course.

### **Essential Elements of a General Purpose Digital Computer**

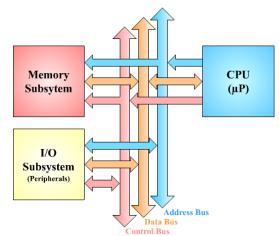

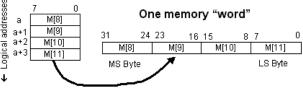

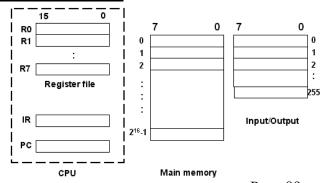

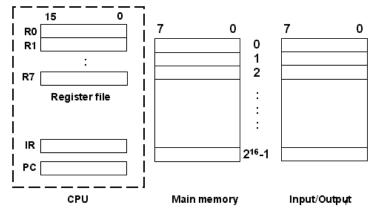

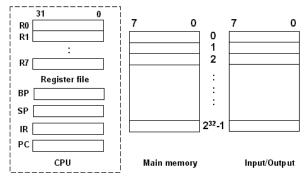

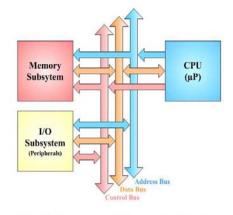

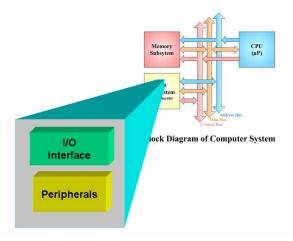

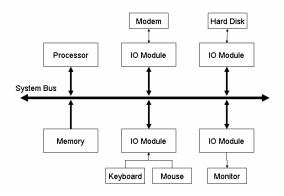

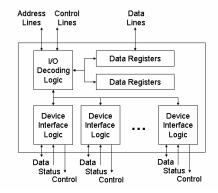

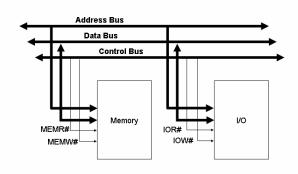

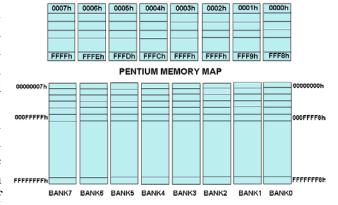

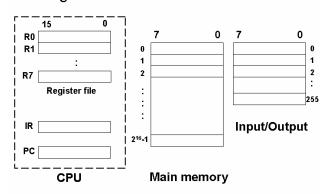

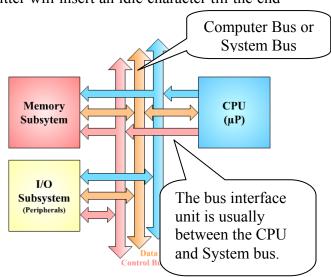

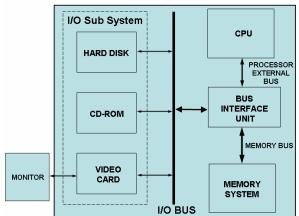

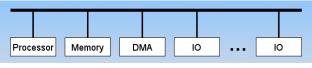

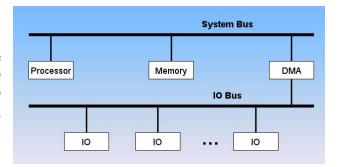

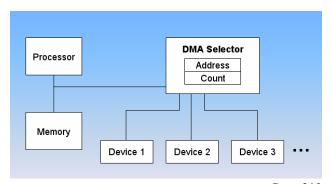

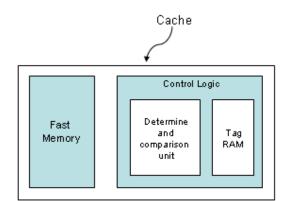

The figure shows the block diagram of a modern general-purpose digital computer.

We observe from the diagram that a general-purpose computer has three main components: memory subsystem, an input/output subsystem, a central processing Programs are stored in the memory, the execution of the program instructions takes place in the CPU. and the communication with the external world is achieved through the I/O subsystem (including the peripherals).

**Block Diagram of a Computer System**

#### Architecture

Now that we understand the term "computer" in our context, let us focus on the term architecture. The word architecture, as defined in standard dictionaries, is "the art or science of building", or "a method or style of building". [2]

### **Computer Architecture**

This term was first used in 1964 by Amdahl, Blaauw, and Brooks at IBM [3]. They defined it as

"the structure of a computer that a machine language programmer must understand to write a correct (time independent) program for that machine."

By architecture, they meant the programmer visible portion of the instruction set. Thus, a

family of machines of the same architecture should be able to run the same software (instructions). This concept is now so common that it is taken for granted. The x86 architecture is a well-known example.

The study of computer architecture includes

- a study of the structure of a computer

- a study of the instruction set of a computer

- a study of the process of designing a computer

### Computer Organization versus Computer Architecture

It is difficult to make a sharp distinction between these two. However, architecture refers to the attributes of a computer that are visible to a programmer, including

- The instruction set

- The number of bits used to represent various data types

- I/O mechanisms

- Memory addressing modes, etc.

On the other hand, organization refers to the operational units of a computer and their interconnections that realize the architectural specifications. These include

- The control signals

- Interfaces between the computer and its peripherals

- Memory technology used, etc.

It is an architectural issue whether a computer will have a specific instruction or not, while it is an organizational issue how that instruction will be implemented.

### **Computer Architect**

We can conclude from the discussion above that a computer architect is a person who designs computers.

#### Design

Design is defined as

### "the process of devising a system, component, or process to meet desired needs."

Most people think of design as a "sketch". This is the usage of the term as a noun. However, the standard engineering usage of the term, as is quite evident from the above definition, is as a verb, i.e., "design is a process". A designer works with a set of stated requirements under a number of constraints to produce the best solution for a given problem. Best may mean a "cost-effective" solution, but not always. Additional or alternate requirements, like efficiency, the client or the designer may impose robustness, etc.. Therefore, design is a decision-making process (often iterative in nature), in which the basic sciences, mathematical concepts and engineering sciences are applied to convert a given set of resources optimally to meet a stated objective.

#### **Knowledge base of a computer architect**

There are many people in the world who know how to drive a car; these are the "users" of cars who are familiar with the behavior of a car and how to operate it. In the same way, there are people who can use computers. There are also a number of people in the world who know how to repair a car; these are "automobile technicians". In the same way, we have computer technicians. However, there are a very few people who know how to design a car; these are "automobile designers". In the same way, there are only very few experts in the world who can design computers. In this course, you will learn how to design computers!

These computer design experts are familiar with

- the structure of a computer

- the instruction set of a computer

- the process of designing a computer

as well as few other related things.

At this point, we need to realize that it is not the job of a single person to design a computer from scratch. There are a number of levels of computer design. Domain experts of that particular level carry out the design activity for each level. These levels of abstraction of a digital computer's design are explained below.

### **Digital Design: Levels of Abstraction**

#### Processor-Memory-Switch level (PMS level)

The highest is the processor-memory-switch level. This is the level at which an architect views the system. It is simply a description of the system components and their interconnections. The components are specified in the form of a block diagram.

#### Instruction Set Level

The next level is instruction set level. It defines the function of each instruction. The emphasis is on the behavior of the system rather than the hardware structure of the system.

#### Register Transfer Level

Next to the ISA (instruction set architecture) level is the register transfer level. Hardware structure is visible at this level. In addition to registers, the basic elements at this level are multiplexers, decoders, buses, buffers etc.

### The above three levels relate to "system design".

### Logic Design Level

The logic design level is also called the gate level. The basic elements at this level are gates and flip-flops. The behavior is less visible, while the hardware structure predominates.

The above level relates to "logic design".

#### Circuit Level

The key elements at this level are resistors, transistors, capacitors, diodes etc.

#### Mask Level

The lowest level is mask level dealing with the silicon structures and their layout that implement the system as an integrated circuit.

### The above two levels relate to "circuit design".

The focus of this course will be the register transfer level and the instruction set level, although we will also deal with the PMS level and the Logic Design Level.

#### **Objectives of the course**

This course will provide the students with an understanding of the various levels of studying computer architecture, with emphasis on instruction set level and register transfer level. They will be able to use basic combinational and sequential building blocks to design larger structures like ALUs (Arithmetic Logic Units), memory subsystems, I/O subsystems etc. It will help them understand the various approaches used to design computer CPUs (Central Processing Units) of the RISC (Reduced Instruction Set Computers) and the CISC (Complex Instruction Set Computers) type, as well as the

principles of cache memories.

### Important topics to be covered

• Review of computer organization

- Classification of computers and their instructions

- Machine characteristics and performance

- Design of a Simple RISC Computer: the SRC

- Advanced topics in processor design

- Input-output (I/O) subsystems

- Arithmetic Logic Unit implementation

- Memory subsystems

### **Course Outline**

#### Introduction:

- Distinction between Computer Architecture, Organization and design

- Levels of abstraction in digital design

- Introduction to the course topics

### **Brief review of computer organization:**

- Perspectives of different people about computers

- General operation of a stored program digital computer

- The Fetch Execute process

- Concept of an ISA

### Foundations of Computer Architecture:

- A taxonomy of computers and their instructions

- Instruction set features

- Addressing Modes

- RISC and CISC architectures

- Measures of performance

#### An example processor: The SRC:

- Introduction to the ISA and instruction formats

- Coding examples and Hand assembly

- Using Behavioral RTL to describe the SRC

- Implementing Register Transfers using Digital Logic Circuits

### **ISA:** Design and Development

- Outline of the thinking process for ISA design

- Introduction to the ISA of the FALCON A

- Solved examples for FALCON-A

- Learning Aids for the FALCON-A

### Other example processors:

- FALCON-E

- EAGLE and Modified EAGLE

- Comparison of the four ISAs

### **CPU Design:**

- The Design Process

- A Uni-Bus implementation for the SRC

- Structural RTL for the SRC instructions

- Logic Design for the 1-Bus SRC

- The Control Unit

- The 2-and 3-Bus Processor Designs

- The Machine Reset

- Machine Exceptions

#### Term Exam – I

### Advanced topics in processor design:

- Pipelining

- Instruction-Level Parallelism

- Microprogramming

### Input-output (I/O):

- I/O interface design

- Programmed I/O

- Interrupt driven I/O

- Direct memory access (DMA)

#### Term Exam – II

### Arithmetic Logic Shift Unit (ALSU) implementation:

- Addition, subtraction, multiplication & division for integer unit

- Floating point unit

### **Memory subsystems:**

- Memory organization and design

- Memory hierarchy

- Cache memories

- Virtual memory

#### References

- [1] Shelly G.B., Cashman T.J., Waggoner G.A., Waggoner W.C., Complete Computer Concepts: Microcomputer and Applications. Ferncroft Village Danvers, Massachusetts: Boyd & Fraser, 1992.

- [2] Merriam-Webster Online; The Language Centre, May 12, 2003 ( <a href="http://www.m-w.com/home.htm">http://www.m-w.com/home.htm</a>).

- [3] Patterson, D.A. and Hennessy, J.L., Computer Architecture- A Quantitative Approach, 2<sup>nd</sup> ed., San Francisco, CA: Morgan Kauffman Publishers Inc., 1996.

- [4] Heuring V.P. and Jordan H.F., Computer Systems Design and Architecture. Melano Park, CA: Addison Wesley, 1997.

A brief review of Computer Organization Perceptions of Different People about Computers

There are various perspectives that a computer can take depending on the person viewing

it. For example, the way a child perceives a computer is quite different from how a computer programmer or a designer views it. There are a number of perceptions of the computer, however, for the purpose of understanding the machine, generally the following four views are considered.

### The User's View

A user is the person for whom the machine is designed, and who employs it to perform some useful work through application software. This useful work may be composing some reports in word processing software, maintaining credit history in a spreadsheet, or even developing some application software using high-level languages such as C or Java. The list of "useful work" is not all-inclusive. Children playing games on a computer may argue that playing games is also "useful work", maybe more so than preparing an internal office memo.

At the user's level, one is only concerned with things like speed of the computer, the storage capacity available, and the behavior of the peripheral devices. Besides performance, the user is not involved in the implementation details of the computer, as the internal structure of the machine is made obscure by the operating system interface.

### The Programmer's View

By "programmer" we imply machine or assembly language programmer. The machine or the assembly language programmer is responsible for the implementation of software required to execute various commands or sequences of commands (programs) on the computer. Understanding some key terms first will help us better understand this view, the associated tasks, responsibilities and tools of the trade.

### **Machine Language**

Machine language consists of all the primitive instructions that a computer understands and is able to execute. These are strings of 1s and 0s.Machine language is the computer's native language. Commands in the machine language are expressed as strings of 1s and 0s. It is the lowest level language of a computer, and requires no further interpretation.

#### **Instruction Set**

A collection of all possible machine language commands that a computer can understand and execute is called its instruction set. Every processor has its own unique instruction set. Therefore, programs written for one processor will generally not run on another processor. This is quite unlike programs written in higher-level languages, which may be portable. Assembly/machine languages are generally unique to the processors on which they are run, because of the differences in computer architecture.

Three ways to list instructions in an instruction set of a computer:

- by function categories

- by an alphabetic ordering of mnemonics

- by an ascending order of op-codes

### **Assembly Language**

Since it is extremely tiring as well as error-prone to work with strings of 1s and 0s for writing entire programs, assembly language is used as a substitute symbolic representation using "English like" key words called mnemonics. A pure assembly language is a language in which each statement produces exactly one machine instruction, i.e. there is a one-to-one correspondence between machine instructions and statements in the assembly language. However, there are a few exceptions to this rule, the

Pentium jump instruction shown in the table below serves as an example.

#### Example

The table provides us with some assembly statement and the machine language

equivalents of the Intel x 86 processor families.

Alpha is a label, and its value will be determined by the position of the jmp instruction in the program and the position of the instruction whose address is alpha. So the second byte in the last instruction can be different for different programs.

| Assembly<br>Language | Mac hine Language<br>(Binary) | Mac hine<br>Language<br>(Hex) | Instruction<br>type |

|----------------------|-------------------------------|-------------------------------|---------------------|

| add cx, dx           | 0000 0001 1101 0001           | 01 D1                         | Arithmetic          |

| mov alx, 34h         | 1011 1000 0011 0100 0000 0000 | B8 34 00                      | Data transfer       |

| xor ax, bx           | 0011 0001 1101 1000           | 31 D8                         | Logic               |

| jmop alloha          | 1110 1011 1111 1100           | EBFC                          | Control             |

Hence there is a one-to-many correspondence of the assembly to machine language in this instruction.

### **Users of Assembly Language**

### • The machine designer

The designer of a new machine needs to be familiar with the instruction sets of other machines in order to be able to understand the trade-offs implicit in the design of those instruction sets.

### • The compiler writer

A compiler is a program that converts programs written in high-level languages to machine language. It is quite evident that a compiler writer must be familiar with the machine language of the processor for which the compiler is being designed. This understanding is crucial for the design of a compiler that produces correct and optimized code.

### • The writer of time or space critical code

A complier may not always produce optimal code. Performance goals may force program-specific optimizations in the assembly language.

### • Special purpose or embedded processor programmer

Higher-level languages may not be appropriate for programming special purpose or embedded processors that are now in common use in various appliances. This is because the functionality required in such applications is highly specialized. In such a case, assembly language programming is required to implement the required functionality.

### Useful tools for assembly language programmers

#### • The assembler:

Programs written in assembly language require translation to the machine language, and an assembler performs this translation. This conversion process is termed as the assembly process. The assembly process can be done manually as well, but it is very tedious and error-prone.

An "assembler" that runs on one processor and translates an assembly language program written for another processor into the machine language of the other processor is called a "cross assembler".

#### • The linker:

When developing large programs, different people working at the same time can develop separate modules of functionality. These modules can then be 'linked' to

form a single module that can be loaded and executed. The modularity of programs, that the linking step in assembly language makes possible, provides the same convenience as it does in higher-level languages; namely abstraction and separation of concerns. Once the functionality of a module has been verified for

correctness, it can be re-used in any number of other modules. The programmer can focus on other parts of the program. This is the so-called "modular" approach, or the "top-down" approach.

### • The debugger or monitor:

Assembly language programs are very lengthy and non-intuitive, hence quite tedious and error-prone. There is also the disadvantage of the absence of an operating system to handle run-time errors that can often crash a system, as opposed to the higher-level language programming, where control is smoothly returned to the operating system. In addition to run-time errors (such as a divide-by-zero error), there are syntax or logical errors.

A "debugger", also called a "monitor", is a computer program used to aid in detecting these errors in a program. Commonly, debuggers provide functionality such as

- o The display and altering of the contents of memory, CPU registers and flags

- Disassembly of machine code (translating the machine code back to assembly language)

- Single stepping and breakpoints that allow the examination of the status of the program and registers at desired points during execution.

While syntax errors and many logical errors can be detected by using debuggers, the best debugger in the world can catch not every logical error.

### • The development system

The development system is a complete set of (hardware and software) tools available to the system developer. It includes

- Assemblers

- Linkers and loaders

- Debuggers

- Compilers

- o Emulators

- Hardware-level debuggers

- Logic analyzers, etc.

### Difference between Higher-Level Languages and Assembly Language

Higher-level languages are generally used to develop application software. These high-level programs are then converted to assembly language programs using compilers. So it is the task of a compiler writer to determine the mapping between the high-level-language constructs and assembly language constructs. Generally, there is a "many-to-many" mapping between high-level languages and assembly language constructs. This means that a given HLL construct can generally be represented by many different equivalent assembly language constructs. Alternately, a given assembly language construct can be represented by many different equivalent HLL constructs.

High-level languages provide various primitive data types, such as integer, Boolean and a string, that a programmer can use. Type checking provides for the verification of proper

usage of these data types. It allows the compiler to determine memory requirements for variables and helping in the detection of bad programming practices.

On the other hand, there is generally no provision for type checking at the machine level, and hence, no provision for type checking in assembly language. The machine only sees strings of bits. Instructions interpret the strings as a type, and it is usually limited to signed or unsigned integers and floating point numbers. A given 32-bit word might be an

instruction, an integer, a floating-point number, or 4 ASCII characters. It is the task of the compiler writer to determine how high-level language data types will be implemented using the data types available at the machine level, and how type checking will be implemented.

### **The Stored Program Concept**

This concept is fundamental to all the general-purpose computers today. It states that the program is stored with data in computer's memory, and the computer is able to manipulate it as data. For example, the computer can load the program from disk, move it around in memory, and store it back to the disk.

Even though all computers have unique machine language instruction sets, the 'stored program' concept and the existence of a 'program counter' is common to all machines.

The sequence of instructions to perform some useful task is called a program. All of the digital computers (the general purpose machine defined above) are able to store these sequences of instructions as stored programs. Relevant data is also stored on the computer's secondary memory. These stored programs are treated as data and the computer is able to manipulate them, for example, these can be loaded into the memory for execution and then saved back onto the storage.

### **General Operation of a Stored Program Computer**

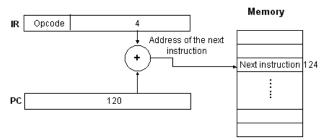

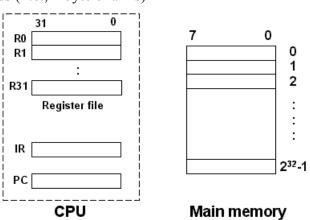

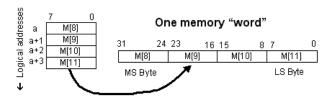

The machine language programs are brought into the memory and then executed instruction by instruction. Unless a branch instruction is encountered, the program is executed in sequence. The instruction that is to be executed is fetched from the memory and temporarily stored in a CPU register, called the instruction register (IR). The instruction register holds the instruction while it is decoded and executed by the central processing unit (CPU) of the computer. However, before loading an instruction into the instruction register for execution, the computer needs to know which instruction to load. The program counter (PC), also called the instruction pointer in some texts, is the register that holds the address of the next instruction in memory that is to be executed.

When the execution of an instruction is completed, the contents of the program counter (which is the address of the next instruction) are placed on the address bus. The memory places the instruction on the corresponding address on the data bus. The CPU puts this instruction onto the IR (instruction register) to decode and execute. While this instruction is decoded, its length in bytes is determined, and the PC (program counter) is incremented by the length, so that the PC will point to the next instruction in the memory. Note that the length of the instruction is not determined in the case of RISC machines, as the instruction length is fixed in these architectures, and so the program counter is always incremented by a fixed number. In case of branch instructions, the contents of the PC are replaced by the address of the next instruction contained in the present branch instruction, and the current status of the processor is stored in a register called the **Processor Status Word** (PSW). Another name for the PSW is the flag register. It contains the status bits, and control bits corresponding to the state of the processor. Examples of status bits include the sign bit, overflow bit, etc. Examples of control bits include interrupt enable flag, etc. When the execution of this instruction is completed, the contents of the program counter are placed on the address bus, and the entire cycle is repeated. This entire process of reading memory, incrementing the PC, and decoding the instruction is known as the **Fetch and Execute** principle of the stored program computer. This is actually an oversimplified situation. In case of the advanced processors of this age, a lot more is going on than just the simple "fetch and execute" operation, such as

pipelining etc. The details of some of these more involved techniques will be studied later on during the course.

### The Concept of Instruction Set Architecture (ISA)

Now that we have an understanding of some of the relevant key terms, we revert to the assembly language programmer's perception of the computer. The programmer's view is limited to the set of all the assembly instructions or commands that can the particular computer at hand execute understood/, in addition to the resources that these instructions may help manage. These resources include the memory space and the entire programmer accessible registers. Note that we use the term 'memory space' instead of memory, because not all the memory space has to be filled with memory chips for a particular implementation, but it is still a resource available to the programmer.

This set of instructions or operations and the resources together form the instruction set architecture (ISA). It is the ISA, which serves as an interface between the program and the functional units of a computer, i.e., through which, the computer's resources, are accessed and controlled.

### The Computer Architect's View

The computer architect's view is concerned with the design of the entire system as well as ensuring its optimum performance. The optimality is measured against some quantifiable objectives that are set out before the design process begins. These objectives are set on the basis of the functionality required from the machine to be designed. The computer architect

- Designs the ISA for optimum programming utility as well as for optimum performance of implementation

- Designs the hardware for best implementation of instructions that are made available in the ISA to the programmer

- Uses performance measurement tools, such as benchmark programs, to verify that the performance objectives are met by the machine designed

- Balances performance of building blocks such as CPU, memory, I/O devices, and interconnections

- Strives to meet performance goals at the lowest possible cost

### Useful tools for the computer architect

Some of the tools available that facilitate the design process are

- Software models, simulators and emulators

- Performance benchmark programs

- Specialized measurement programs

- Data flow and bottleneck analysis

- Subsystem balance analysis

- Parts, manufacturing, and testing cost analysis

### The Logic Designer's View

The logic designer is responsible for the design of the machine at the logic gate level. It is the design process at this level that determines whether the computer architect meets cost and performance goals. The computer architect and the logic designer have to work in collaboration to meet the cost and performance objectives of a machine. This is the reason why a single person or a single team may be performing the tasks of system's architectural design as well as the logic design.

### **Useful Tools for the Logic Designer**

Some of the tools available that aid the logic designer in the logic design process are

- CAD tools

- Logic design and simulation packages

- Printed circuit layout tools

- IC (integrated circuit) design and layout tools

- Logic analyzers and oscilloscopes

- Hardware development systems

### The Concept of the Implementation Domain

The collection of hardware devices, with which the logic designer works for the digital logic gate implementation and interconnection of the machine, is termed as the implementation domain. The logic gate implementation domain may be

- VLSI (very large scale integration) on silicon

- TTL (transistor-transistor logic) or ECL (emitter-coupled logic) chips

- Gallium arsenide chips

- PLAs (programmable-logic arrays) or sea-of-gates arrays

- Fluidic logic or optical switches

Similarly, the implementation domains used for gate, board and module interconnections are

- Poly-silicon lines in ICs

- Conductive traces on a printed circuit board

- Electrical cable

- Optical fiber, etc.

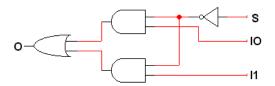

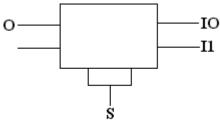

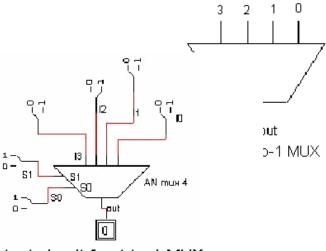

At the lower levels of logic design, the designer is concerned mainly with the functional details represented in a symbolic form. The implementation details are not considered at these lower levels. They only become an issue at higher levels of logic design. An example of two-to-one a multiplexer in various implementation domains will illustrate this point. Figure (a) is the generic logic gate (abstract domain) representation of a 2-to-1 multiplexer.

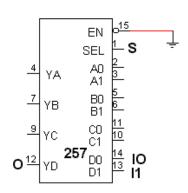

Figure (b) shows the 2-to-1 multiplexer logic gate implementation

(a) Abstract view of Boolean logic

#### (b) TTL implementation domain

in the domain of TTL (VLSI on Silicon) logic using part number '257, with interconnections in the domain of printed circuit board traces.

Figure (c) is the implementation of the 2-to-1 multiplexer with a fiber optic directional coupler switch, which has an interconnection domain of optical fiber.

Classical logic design versus computer logic design 11

( c ) Optical switch implementation

We have already studied the sequential circuit design concepts in the course on Digital Logic Design, and thus are familiar with the techniques used. However, these traditional techniques for a finite state machine are not very practical when it comes to the design of a computer, in spite of the fact that a computer is a finite state machine. The reason is that employing these techniques is much too complex as the computer can assume hundreds of states.

#### **Sequential Logic Circuit Design**

When designing a sequential logic circuit, the problem is first coded in the form of a state diagram. The redundant states may be eliminated, and then the state diagram is translated into the next state table. The minimum number of flip-flops needed to implement the design is calculated by making "state assignments" in terms of the flip-flop "states". A "transition table" is made using the state assignments and the next state table. The flip-flop control characteristics are used to complete a set of "excitation tables". The excitation equations are determined through minimization. The logic circuit can then be drawn to implement the design. A detailed discussion of these steps can be found in most books on Logic Design.

### **Computer Logic Design**

Traditional Finite State Machine (FSM) design techniques are not suitable for the design of computer logic. Since there is a natural separation between the data path and the control path in case of a digital computer, a modular approach can be used in this case.

The data path consists of the storage cells, the arithmetic and logic components and their interconnections. Control path is the circuitry that manages the data path information flow. So considering the behavior first can carry out the design. Then the structure can be considered and dealt with. For this purpose, well-defined logic blocks such as multiplexers, decoders, adders etc. can be used repeatedly.

### Two Views of the CPU Program Counter Register

The view of a logic designer is more detailed than that of a programmer. Details of the mechanism used to control the machine are unimportant to the programmer, but of vital importance to the logic designer. This can be illustrated through the following two views of the program counter of a machine.

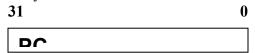

As shown in figure (a), to a programmer the program counter is just a register, and in this case, of length 32 bits or 4 bytes.

### (a) Program Counter: Programmer's view

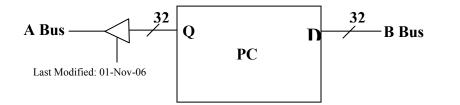

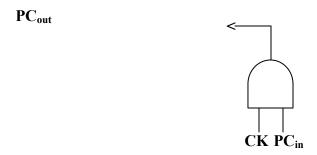

Figure (b) illustrates the logic designer's view of a 32-bit program counter, implemented as an array of 32 D flip-flops. It shows the contents of the program counter being gated out on 'A bus' (the address bus) by applying a control signal  $PC_{out}$ . The contents of the 'B bus' (also the address bus), can be stored in the program counter by asserting the signal  $PC_{in}$  on the leading edge of the clock signal CK, thus storing the address of the next instruction in the program counter.

(b) Program Counter: Logic Designer's View

#### Lecture Handout

# **Computer Architecture**

### Lecture No. 2

#### **Reading Material**

Vincent P. Heuring&Harry F. Jordan Computer Systems Design and Architecture Chapter 2, Chapter 3 2.1, 2.2, 3.2

#### Summary

- 1) A taxonomy of computers and their instructions

- 2) Instruction set features

- 3) Addressing modes

- 4) RISC and CISC architectures

# **Foundations Of Computer Architecture**

#### TAXONOMY OF COMPUTERS AND THEIR INSTRUCTIONS

Processors can be classified on the basis of their instruction set architectures. The instruction set architecture, described in the previous module gives us a 'programmer's view' of the machine. This module discussed a number of topics related to the classifications of computers and their instructions.

#### CLASSES OF INSTRUCTION SET ARCHITECTURE:

The mechanism used by the CPU to store instructions and data can be used to classify the ISA (Instruction Set Architecture). There are three types of machines based on this classification.

- Accumulator based machines

- Stack based machines

- General purpose register (GPR) machines

#### ACCUMULATOR BASED MACHINES

Accumulator based machines use special registers called the accumulators to hold one source operand and also the result of the arithmetic or logic operations performed. Thus the accumulator registers collect (or 'accumulate') data. Since the accumulator holds one of the operands, one more register may be required to hold the address of another operand. The accumulator is not used to hold an address. So accumulator based machines are also called 1-address machines. Accumulator machines employ a very small number

of accumulator registers, generally only one. These machines were useful at the time when memory was quite expensive; as they used one register to hold the source operand

as well as the result of the operation. However, now that the memory is relatively inexpensive, these are not considered very useful, and their use is severely limited for the computation of expressions with many operands.

### STACK BASED MACHINES

A stack is a group of registers organized as a last-in-first-out (LIFO) structure. In such a structure, the operands stored first, through the push operation, can only be accessed last, through a pop operation; the order of access to the operands is reverse of the storage operation. An analogy of the stack is a "plate-dispenser" found in several self-service cafeterias. Arithmetic and logic operations successively pick operands from the top-of-the-stack (TOS), and push the results on the TOS at the end of the operation. In stack based machines, operand addresses need not be specified during the arithmetic or logical operations. Therefore, these machines are also called 0-address machines.

### GENERAL-PURPOSE-REGISTER MACHINES

In general purpose register machines, a number of registers are available within the CPU. These registers do not have dedicated functions, and can be employed for a variety of purposes. To identify the register within an instruction, a small number of bits are required in an instruction word. For example, to identify one of the 64 registers of the CPU, a 6-bit field is required in the instruction.

CPU registers are faster than cache memory. Registers are also easily and more effectively used by the compiler compared to other forms of internal storage. Registers can also be used to hold variables, thereby reducing memory traffic. This increases the execution speed and reduces code size (fewer bits required to code register names compared to memory). In addition to data, registers can also hold addresses and pointers (i.e., the address of an address). This increases the flexibility available to the programmer.

A number of dedicated, or special purpose registers are also available in general-purpose machines, but many of them are not available to the programmer. Examples of transparent registers include the stack pointer, the program counter, memory address register, memory data register and condition codes (or flags) register, etc.

We should understand that in reality, most machines are a combination of these machine types. Accumulator machines have the advantage of being more efficient as these can store intermediate results of an operation within the CPU.

### **INSTRUCTION SET**

An instruction set is a collection of all possible machine language commands that are understood and can be executed by a processor.

### ESSENTIAL ELEMENTS OF COMPUTER INSTRUCTIONS:

There are four essential elements of an instruction; the type of operation to be performed, the place to find the source operand(s), the place to store the result(s) and the source of the next instruction to be executed by the processor.

#### Type of operation

In module 1, we described three ways to list the instruction set of a machine; one way of enlisting the instruction set is by grouping the instructions in accordance with the functions they perform. The type of operation that is to be performed can be encoded in

the op-code (or the operation code) field of the machine language instruction. Examples of operations are mov, jmp, add; these are the assembly mnemonics, and should not be

confused with op-codes. Op-codes are simply bit-patterns in the machine language format of an instruction.

#### Place to find source operands

An instruction needs to specify the place from where the source operands will be retrieved and used. Possible locations of the source operands are CPU registers, memory cells and I/O locations. The source operands can also be part of an instruction itself; such operands are called immediate operands.

#### Place to store the results

An instruction also specifies the location in which the result of the operation, specified by the instruction, is to be stored. Possible locations are CPU registers, memory cells and I/O locations.

### Source of the next instruction

By default, in a program the next instruction in sequence is executed. So in cases where the next-in-sequence instruction execution is desired, the place of next instruction need not be encoded within the instruction, as it is implicit. However, in case of a branch, this information needs to be encoded in the instruction. A branch may be conditional or unconditional, a subroutine call, as well as a call to an interrupt service routine.

### Example

The table provides examples of assembly language commands and their machine

language equivalents. In the instruction add cx, dx, the contents of the location dx are added to the contents of the location cx, and the result is stored in cx. The instruction type is arithmetic, and the op-code for the add instruction is 0000, as shown in this example.

| Assembly<br>Language | Mac hine Language<br>(Binary) | Mac hine<br>Language<br>(Hex) | Instruction<br>type |

|----------------------|-------------------------------|-------------------------------|---------------------|

| add cx, dx           | 0000 0001 1101 0001           | 01 D1                         | Arithmetic          |

| mov al, 34h          | 1011 1000 0011 0100 0000 0000 | B8 34 00                      | Data transfer       |

| xor ax, b x          | 0011 0001 1101 1000           | 31 D8                         | Logic               |

| jmp alpha            | 1110 1011 1111 1100           | EBFC                          | Control             |

#### CLASSIFICATIONS OF

#### **INSTRUCTIONS:**

We can classify instructions according to the format shown below.

- 4-address instructions

- 3-address instructions

- 2-address instructions

- 1-address instructions

- 0-address instructions

The distinction is based on the fact that some operands are accessed from memory, and therefore require a memory address, while others may be in the registers within the CPU or they are specified implicitly.

### 4-address instructions

The four address instructions specify the addresses of two source operands, the address of the destination operand and the next instruction address.

4-address instructions are not very common because the next

| op code | destination | source 1 | source 2 | next address |

|---------|-------------|----------|----------|--------------|

|         |             |          |          |              |

instruction to be executed is sequentially stored next to the current instruction in the

memory. Therefore, specifying its address is redundant. These instructions are used in the micro-coded control unit, which will be studied later.

#### 3-address instruction

3-address Α instruction specifies the addresses of two operands and the address of the destination operand.

| op code | destination | source 1 | source 2 |

|---------|-------------|----------|----------|

|---------|-------------|----------|----------|

#### 2-address instruction

A 2-address instruction has three fields; one for the op-code, the second field specifies the address of one of the source operands as well as the destination operand, and the last field is used for holding the address of the

|         |             | *        |

|---------|-------------|----------|

| op code | destination | source 2 |

|         | source 1    |          |

second source operand. So one of the fields serves two purposes; specifying a source operand address and a destination operand address.

#### 1-address instruction

A 1-address instruction has a dedicated CPU register,

called the accumulator, to hold one operand and to store

| op code | source 2 |

|---------|----------|

|         |          |

the result. There is no need of encoding the address of the accumulator register to access the operand or to store the result, as its usage is implicit. There are two fields in the instruction, one for specifying a source operand address and a destination operand address.

#### 0-address instruction

A 0-address instruction uses a stack to hold both the operands and the result. Operations are performed on the operands stored on the top of the stack and the second value on the stack. The result is stored on the top of the stack. Just like the use of an accumulator register, the addresses of

| ор | code |  |

|----|------|--|

|    |      |  |

the stack registers need not be specified, their usage is implicit. Therefore, only one field is required in 0-address instruction; it specifies the op-code.

### COMPARISON OF INSTRUCTION FORMATS:

### **Basis for comparison**

Two parameters are used as the basis for comparison of the instruction sets discussed above. These are

- Code size Code size has an effect on the storage requirements for the instructions; the greater the code size, the larger the memory required.

- Number of memory accesses

Page 33 Last Modified: 01-Nov-06

The number of memory accesses has an effect on the execution time of instructions; the greater the number of memory accesses, the larger the time required for the execution cycle, as memory accesses are generally slow.

### **Assumptions**

We make a few assumptions, which are

- A single byte is used for the op code, so 256 instructions can be encoded using these 8 bits, as  $2^8 = 256$

- The size of the memory address space is 16 Mbytes

- A single addressable memory unit is a byte

- Size of operands is 24 bits. As the memory size is 16Mbytes, with byte-addressable memory, 24 bits are required to encode the address of the operands.

- The size of the address bus is 24 bits

- Data bus size is 8 bits

### **Discussion4-address instruction**

| • | The code size is 13 bytes                       | op code | destination | source 1 | source 2 | next address |

|---|-------------------------------------------------|---------|-------------|----------|----------|--------------|

| • | (1+3+3+3+3<br>= 13 bytes)<br>Number of<br>bytes | 1 byte  | 3 bytes     | 3 bytes  | 3 bytes  | 3 bytes      |

accessed from memory is 22 (13 bytes for instruction fetch + 6 bytes for source operand fetch + 3 bytes for storing destination operand = 22 bytes)

Note that there is no need for an additional memory access for the operand corresponding to the next instruction, as it has already been brought into the CPU during instruction fetch.

#### 3-address instruction

| • | The code size is 10 bytes | op code | destination |

|---|---------------------------|---------|-------------|

|   | (1+3+3+3=10  bytes)       |         |             |

|   | (1131313 10 bytes)        |         |             |

• Number of bytes accessed from memory is 22

| op 0000 | 400111411011 |         | 004.00 2 |

|---------|--------------|---------|----------|

| 1 byte  | 3 bytes      | 3 bytes | 3 bytes  |

source 1

source 2

(10 bytes for instruction fetch + 6 bytes for source operand fetch + 3 by

+ 6 bytes for source operand fetch + 3 bytes for storing destination operand = 19 bytes)

#### 2-address instruction

• The code size is 7 bytes (1+3+3 = 7 bytes)

op code destination source 2 source 1

Number of bytes accessed from memory is 16(7 bytes for instruction fetch + 6 bytes for source operand fetch + 3 bytes for storing destination of

1 byte 3 bytes 3 bytes

fetch + 3 bytes for storing destination operand = 16 bytes)

# bytes) 1-address instruction op code | source 2

### • The code size is 4 bytes (1+3= 4 bytes)

• The code size is 4 bytes (1+3-4 bytes)

• Number of bytes accessed from memory is 7 (4 bytes for instruction fetch + 3 bytes for source

| 1 byte | 3 bytes |

|--------|---------|

|        |         |

operand fetch + 0 bytes for storing destination operand = 7 bytes)

#### 0-address instruction

• The code size is 1 byte

| • | Number | of bytes | accessed | from | memory | is | 10 | į |

|---|--------|----------|----------|------|--------|----|----|---|

|---|--------|----------|----------|------|--------|----|----|---|

(1 byte for instruction fetch + 6 bytes for source operand fetch + 3 bytes for storing destination operand = 10 bytes)

| _ |      |  |

|---|------|--|

| 1 | byte |  |

|   |      |  |

op code

The following table summarizes this information

### HALF ADDRESSES

In the preceding discussion we have talked about memory addresses. This discussion also applies to CPU registers. However, to specify/ encode a CPU register, less number of bits is

| Instruction Format    | Code<br>size | Number of memory bytes |

|-----------------------|--------------|------------------------|

| 4-address instruction | 13           | 22                     |

| 3-address instruction | 10           | 19                     |

| 2-address instruction | 7            | 16                     |

| 1-address instruction | 4            | 7                      |

| 0-address instruction | 1            | 10                     |

required as compared to the memory addresses. Therefore, these addresses are also called "half-addresses". An instruction that specifies one memory address and one CPU register can be called as a  $1\frac{1}{2}$ -address instruction

### **Example**

mov al, [34h]

### THE PRACTICAL SITUATION

Real machines are not as simple as the classifications presented above. In fact, these machines have a mixture of 3, 2, 1, 0, and 1½-address instructions. For example, the VAX 11 includes instructions from all classes.

# CLASSIFICATION OF MACHINES ON THE BASIS OF OPERAND AND RESULT LOCATION:

A distinction between machines can be made on the basis of the ALU instructions; whether these instructions use data from the memory or not. If the ALU instructions use only the CPU registers for the operands and result, the machine type is called "load-store". Other machines may have a mixture of register-memory, or memory-memory instructions.

The number of memory operands supported by a typical ALU instruction may vary from 0 to 3.

### **Example**

The SPARC, MIPS, Power PC, ALPHA: 0 memory addresses, max operands allowed = 3 X86, 68x series: 1 memory address, max operands allowed = 2

#### LOAD- STORE MACHINES

These machines are also called the register-to-register machines. They typically use the 1½ address instruction format. Only the load and store instructions can access the memory. The load instruction fetches the required data from the memory and temporarily stores it in the CPU registers. Other instructions may use this data from the CPU registers. Then later, the results can be stored back into the memory by the store instruction. Most RISC computers fall under this category of machines.

### **Advantages (of register-register instructions)**

Register-register instructions use 0 memory operands out of a total of 3 operands. The advantages of such a scheme is:

• The instructions are simple and fixed in length

- The corresponding code generation model is simple

- All instructions take similar number of clock cycles for execution

### **Disadvantages (register-register instructions)**

- The instruction count is higher; the number of instructions required to complete a particular task is more as separate instructions will be required for load and store operations of the memory

- Since the instruction size is fixed, the instructions that do not require all fields waste memory bits

### **Register-memory machines**

In register-memory machines, some operands are in the memory and some are in registers. These machines typically employ 1 or 1½ address instruction format, in which one of the operands is an accumulator or a general-purpose CPU registers.

### **Advantages**

Register-memory operations use one memory operand out of a total of two operands. The advantages of this instruction format are

- Operands in the memory can be accessed without having to load these first through a separate load instruction

- Encoding is easy due to the elimination of the need of loading operands into registers first

- Instruction bit usage is relatively better, as more instructions are provided per fixed number of bits

#### Disadvantages

- Operands are not equivalent since one operand may have two functions (both source operand and destination operand), and the source operand may be destroyed

- Different size encoding for memory and registers may restrict the number of registers

- The number of clock cycles per instruction execution vary, depending on the operand location operand fetch from memory is slow as compared to operands in CPU registers

### **Memory-Memory Machines**

In memory-memory machines, all three of the operands (2 source operands and a destination operand) are in the memory. If one of the operands is being used both as a source and a destination, then the 2-address format is used. Otherwise, memory-memory machines use 3-address formats of instructions.

### Advantages

- The memory-memory instructions are the most compact instruction where encoding wastage is minimal.

- As operands are fetched from and stored in the memory directly, no CPU registers are wasted for temporary storage

#### **Disadvantages**

- The instruction size is not fixed; the large variation in instruction sizes makes decoding complex

- The cycles per instruction execution also vary from instruction to instruction

• Memory accesses are generally slow, so too many references cause performance degradation

#### Example 1

The expression a = (b+c)\*d - e is evaluated with the 3, 2, 1, and 0address machines to provide a

| 3-Address   | 2-Address | 1-Address | 0-Address |

|-------------|-----------|-----------|-----------|

| add a, b, c | load a, b | lda b     | push b    |

| mpy a, a, d | add a, c  | add c     | push c    |

| sub a, a, e | mpy a, d  | mpy d     | add       |

|             | sub a, e  | sub e     | push d    |

|             |           | sta a     | mpy       |

|             |           |           | push e    |

|             |           |           | sub       |

|             |           |           | рор а     |

1-Address

; order changed to reduce code size

;add b to acc

;subtract acc from s

0-Address

push 58

push 16

push a

push b

push 4

add

mu1

sub

add

mu1

comparison of their advantages and disadvantages discussed above. The instructions shown in the table are the minimal instructions required to evaluate the given expression. Note that these are not machine language instructions, rather the pseudo-code.

#### Example 2

The instruction z = 4(a + b) - 16(c + 58) is with the 3, 2, 1, and 0-address machines in the table.

add x, a, b

muly, x, 4

add r, c, 58

mul s, r, 16

sub z, y, s

3-Address 2-Address

load y, a

add y, b

mul y, 4

load s, c

add s, 58

muls, 16

sub y, s

store z, y

lda c

adda 58

mula 16

stas

1da a

adda b

mula 4

suba s

staz

of

#### **Functional** classification instruction sets:

Instructions can be classified into the following four categories based on their functionality.

- Data processing

- Data storage (main memory)

- Data movement (I/O)